# nRFgo Starter Kit

User Guide v1.6

## **Contents**

| 1     | Introduction                  | 3  |

|-------|-------------------------------|----|

| 1.1   | Minimum requirements          | 3  |

| 1.2   | Writing Conventions           | 3  |

| 1.3   | Development kit release notes |    |

| 1.4   | Kit content                   |    |

| 2     | nRFgo Motherboard (nRF6310)   | 5  |

| 2.1   | nRF module connectors         |    |

| 2.2   | Power supply                  | 8  |

| 2.2.1 | Regulated supplies            | 9  |

| 2.2.2 | Status LEDs                   | 9  |

| 2.3   | Status display                | 10 |

| 2.4   | nRF reset button              | 10 |

| 2.5   | Ground connection             | 10 |

| 2.6   | I/O port headers              | 10 |

| 2.7   | Buttons                       | 11 |

| 2.8   | LEDs                          | 12 |

| 2.9   | RS232 serial port interface   | 13 |

| 2.10  | ISP interface                 | 14 |

| 2.11  | nRF debug interface           | 15 |

| 2.12  | Extension board connectors    | 17 |

| 2.13  | Block schematic               | 19 |

| 3     | Display module (nRF6350)      | 20 |

| 3.1   | Display description           |    |

| 3.2   | Joystick description          |    |

| 4     | Troubleshooting               | 22 |

#### 1 Introduction

The nRFgo Starter Kit is the core of the nRFgo evaluation and development platform for our ultra low power radios. Used with our nRFgo Development Kits (sold separately), it is the ideal platform for each stage of the development process.

nRFgo Development Kit modules that are included in our nRFgo Development Kits are designed to fit onto the nRFgo Motherboard in the nRFgo Starter Kit.

#### 1.1 Minimum requirements

Listed are minimum hardware and software requirements for using the nRFgo Starter Kit:

- Computer with 2 USB ports

- Windows XP, Windows 7

- nRFgo Studio (a software program available from www.nordicsemi.com)

#### 1.2 Writing conventions

This User Guide follows a set of typographic rules that makes the document consistent and easy to read. The following writing conventions are used:

- Commands are written in Lucida Console.

- Pin names are written in Consolas.

- File names and User Interface components are written in **bold**.

- Internal cross references are italicized and written in semi-bold.

# 1.3 Development kit release notes

| Date         | Version | Description                                                                                                                                                                                                                           |

|--------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 2012 | 2.0     | <ul> <li>Module update</li> <li>nRF6350:         <ul> <li>The display module (nRF6350) has been updated to support the nRF51 series development kits. Changes to the user guide are mainly found in chapter 3.</li> </ul> </li> </ul> |

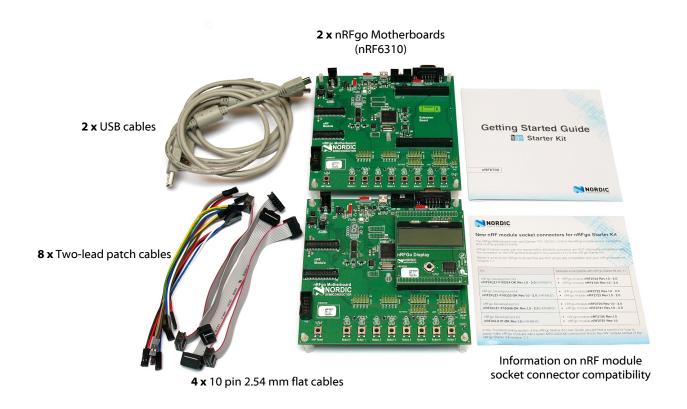

#### 1.4 Kit content

Software and documentation can be downloaded from www.nordicsemi.com.

**Figure 1** nRFgo Starter Kit content

# 2 nRFgo Motherboard (nRF6310)

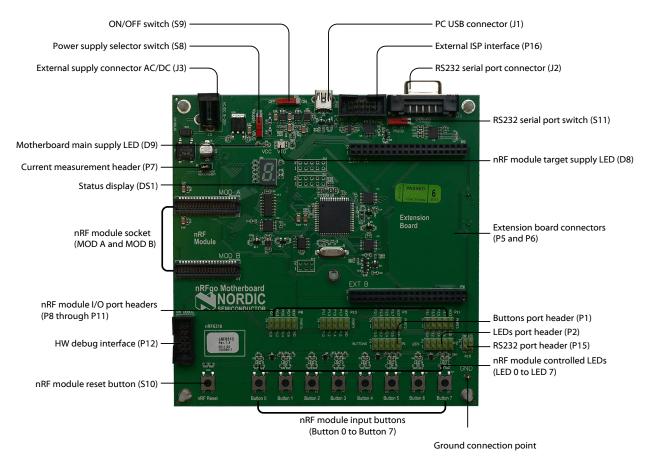

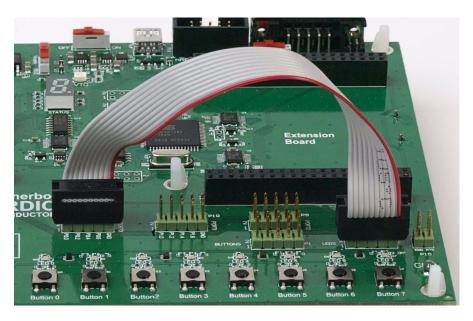

Figure 2 nRFgo Motherboard (nRF6310)

**Note:** On the underside of the Motherboard is a battery holder that takes three AAA batteries.

#### 2.1 nRF module connectors

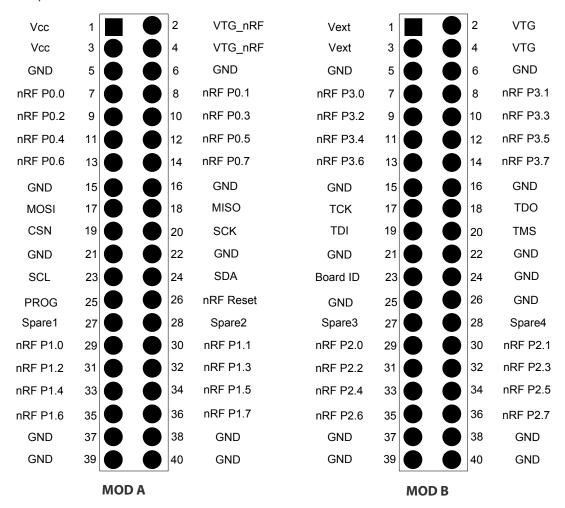

To utilize the features of the Starter Kit, an nRFgo compatible Development Kit module (sold separately) must be inserted into the nRF module socket, see *Figure 3*.

**Figure 3** nRF module connectors

**Note:** Do not apply too much pressure on the antenna end of your Development Kit module when inserting it into the Motherboard, as this may distort the pins in the Motherboard connectors. When removing, pull the module straight up.

The nRF module connectors, MOD A (**P3**) and MOD B (**P4**), have all the I/Os required for communicating with nRFgo compatible modules.

Figure 4 nRF module connectors - MOD A and MOD B

| Pin Number       |                       | MOD B                                                                          | MOD A                                          |                                                                                      |

|------------------|-----------------------|--------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------|

| Pin Number       | Name                  | Function                                                                       | Name                                           | Function                                                                             |

| 1, 3             | Vext                  | Power supply output for circuitry on the Motherboard.                          | VCC                                            | Main power supply of the Motherboard.                                                |

| 2, 4             | VTG                   | Target Power supply for<br>non-nRF device(s) on the<br>Development Kit module. | VTG_nRF                                        | Target Power supply for nRF devices on the Development Kit module.                   |

| 7 - 14           | P3.x                  | nRF device port 3.                                                             | P0.x                                           | nRF device port 0.                                                                   |

| 15 - 16          | GND                   | Ground.                                                                        | GND                                            | Ground.                                                                              |

| 17 - 20          | TCK,TDI,<br>TDO, TMS  | nRF probe hardware debugger JTAG interface.                                    | MOSI,MISO<br>, CSN<br>SCK <sup>1</sup>         | Main MCU SPI control interface for the Motherboard.                                  |

| 21 - 22          | GND                   | Ground.                                                                        | GND                                            | Ground.                                                                              |

| 23               | Board ID <sup>2</sup> | Development Kit ID.                                                            | SCL <sup>1</sup>                               | 2-wire clock from nRFgo<br>Motherboard main MCU.                                     |

| 24               | GND                   | Ground.                                                                        | SDA <sup>1</sup>                               | 2-wire data from the Motherboard main MCU.                                           |

| 25-26 <b>GND</b> |                       | Ground.                                                                        | PROG <sup>2</sup><br>nRF<br>Reset <sup>2</sup> | Motherboard main MCU program enable and reset control of the Development Kit module. |

| 27-28            | Spare x               | Reserved                                                                       | Spare x                                        | Reserved                                                                             |

| 29-36            | P2.x                  | nRF device Port 2                                                              | P1.x                                           | nRF device port 1.                                                                   |

| 37-40            | GND                   | Ground                                                                         | GND                                            | Ground                                                                               |

- 1. Motherboard main MCU control interfaces only. nRF device SPI and 2 wire interfaces (if present) are available in the nRF device ports (pins 7 14 or 29 36).

- 2. Used by the Motherboard only.

**Table 1** Description of the nRF module connector pins

The pinout of each of the generic ports will change depending on which device is present on the Development Kit module. Please refer to the nRF device's Development Kit User Guide for pinout details on the nRF device ports (pins 7 to 14 and 29 to 36).

# 2.2 Power supply

The Motherboard can be powered from three sources:

- USB connected to a computer

- External power supply with the following specifications:

- AC or DC

- 8 to 20 V, min 500 mA.

- 2.1 mm center pin, with any polarity

- Batteries

- 3 x AAA 1.5 V. Do not use rechargeable batteries.

The **S9** switch is the main power switch and allows you to turn the Motherboard on and off.

Using switch **S8** you can select where the Motherboard should receive power; from **VBUS** in the USB connector, or from the external power supply connector **J3**.

**Figure 5** Power supply connection and S8 setting for A: USB and B: External

The **3 x** AAA battery pack supplies the board if neither external power supply options are present. When using batteries the **59** switch is still the main power switch. Setting the **58** switch is no longer relevant.

The regulated supplies on the Motherboard can supply a total of 500 mA. When external application circuitry is connected, ensure that the current drain does not exceed this limit. If a USB is used as the power supply to the system, ensure that the USB port is capable of delivering 500 mA or use an externally powered USB hub.

#### 2.2.1 Regulated supplies

The Motherboard has three separate power nets: VTG, VCC, and VEXT.

**VTG:** Vtarget is the power supply for the Development Kit module. This is a variable power supply controlled through nRFgo Studio, which is available from <a href="www.nordicsemi.com">www.nordicsemi.com</a>. The VTG is split into two branches: VTG and VTG\_nRF. VTG\_nRF is split from VTG and routed through the nRF current measurement header **P7**. On the Development Kit modules VTG\_nRF supplies only the nRF devices. Any non-Nordic Semiconductor circuitry is supplied from VTG. This arrangement enables 'nRF device(s) only' current consumption measurements on **P7**.

**VCC:** Mainly for the Motherboard control circuitry, VCC is a fixed 3.8 V supply. It is available from the nRF module connectors and more importantly in the extension board connectors for development flexibility.

**VEXT:** Directly interfacing the nRF module, VEXT supplies the signal level shifters and circuitry/headers. VEXT on the Motherboard is sourced from the Development Kit module to ensure correct signal levels. In most cases the connector pins VTG and VEXT are shorted on the nRF module resulting in VEXT=VTG. Please refer to the Development Kit User Guides for details.

#### 2.2.2 Status LEDs

The Motherboard has two LEDs indicating power supply status:

- **D9** is lit if VCC is present.

- **D8** is green if VTG is present.

#### 2.3 Status display

When nRFgo Studio is running and the Motherboard is connected to your computer, the LED status display shows the ID number assigned to the Motherboard by nRFgo Studio. The same ID will be shown in the nRFgo Studio user interface. If two or more Motherboards are connected to one computer, make sure the ID number in the nRFgo Studio user interface matches the ID on the Motherboard you want to control.

If you unplug the USB cable linking the Motherboard to your computer, and the board is fitted with batteries, the ID number assigned to the Motherboard will begin to flash intermittently with a dot (.). This signals that the Motherboard's ID may change in nRFgo Studio when the Motherboard is reconnected to your computer.

#### 2.4 nRF reset button

The nRF RESET button is the reset button for the Development Kit module connected to MODA/MODB. Pressing this button causes a full reset of the Development Kit module, but it does not affect the Motherboard's main MCU.

#### 2.5 Ground connection

Apart from the GND found in various headers on the Motherboard, a separate GND connection is available for test instruments.

#### 2.6 I/O port headers

The I/O ports of the Development Kit module are routed directly to the I/O headers (**P8-P11**) on the Motherboard.

Figure 6 General pinout of the I/O port headers

All I/O header pinouts are identical and shown in *Figure 6*. The number of headers and pins used and the pinout will vary depending on which nRFgo development module is fitted. Please refer to each Development Kit User Guide for details.

#### 2.7 Buttons

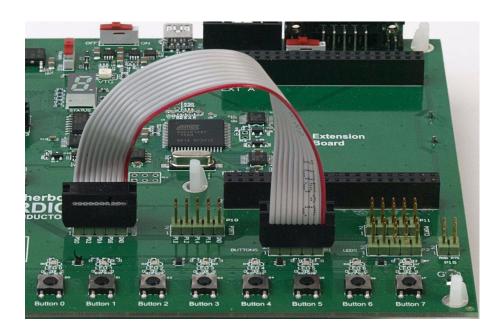

Eight buttons are provided on the Motherboard to offer you a simple way to give device feedback during development. The buttons are connected to the Button header (P1). One of the 10 pin cables supplied in the nRFgo Starter Kit is used to connect the Button header (P1) to the wanted device port or pin found in the I/O headers (P8-P11), illustrated in *Figure 7 on page 11*.

Figure 7 Connection of the Motherboard buttons to an I/O header

Pressing a button provides a 0 V input for the nRF device. Pull up resistors give VEXT levels when the buttons are released. *Figure 8* shows the button circuitry schematic and the button header (**P1**) pinout.

**Figure 8** General pinout of the button headers

#### 2.8 LEDs

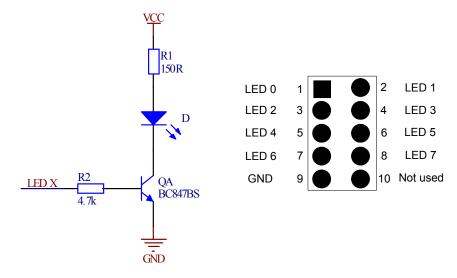

Eight LEDs are provided on the Motherboard to supply you with a simple way to read device output during development. These are fitted with drivers and connected to the LED header (**P2**). The 10 pin cables supplied are used to connect the LED header (**P2**) to the wanted I/O port or pin headers, see *Figure 9*.

Figure 9 Connection of the Motherboard LEDs to an I/O header

Logic high output from an nRF device lights the LEDs. *Figure 10* shows the LEDs circuitry schematic and header **P2** pinout.

Figure 10 LED circuitry schematic and header P2 pinout

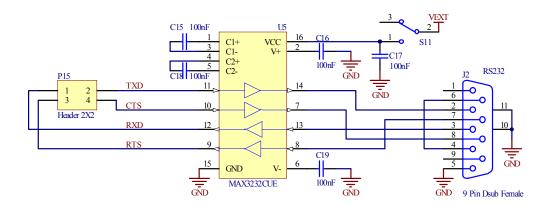

#### 2.9 RS232 serial port interface

The RS232 header (**P15**) is connected to the RS232 serial port interface (**J2**) through a RS232 converter. See *Figure 11* for the schematic. Normally, only TXD (Transmit Data) and RXD (Receive Data) are used, but CTS (Clear to Send) and RTS (Request to Send) can be used for hardware flow control.

Figure 11 RS232 converter schematic

The UART data pins, TXD and RXD, will be present on different I/O port pins depending on the Development Kit; please see each Development Kit User Guide for details. Connect a double or two single cables between **P15** and the correct pins in **P8** to **P11** to use the RS232 converter. *Figure 12* shows a connection example for a nRF24LE1-F16Q48. You must also switch on the RS232 converter with the RS232 serial port switch (**S11**).

Figure 12 RS232 header P15 connected to I/O header

| Pin number | Signal name | Description         |

|------------|-------------|---------------------|

| 1          | RXD         | UART receives data  |

| 2          | TXD         | UART transmits data |

| 3          | RTS         | Request to send     |

| 4          | CTS         | Clear to send       |

Table 2 UART header P15 pin description

#### 2.10 ISP interface

A nRF ISP interface (**P16**) is available on the Motherboard to enable in-circuit programming (ISP) of nRF devices. This interface enables ISP on your application boards. *Figure 13* shows the pinout of the ISP connector. Please refer to nRF device product specifications for details on the program interface pinout on each nRF device.

**Note:** You must manually enable the nRF ISP interface in nRFgo Studio before you can use it for ISP on an application board external to the Motherboard.

Figure 13 nRF ISP interface pinout

| Pin number | Signal name | Description                                         |  |

|------------|-------------|-----------------------------------------------------|--|

| 1          | RF_VDD      | Supply voltage from the connected application board |  |

| 2          |             | Not used                                            |  |

| 3          | PROG        | Program enable                                      |  |

| 4          | CSN         | SPI chip select                                     |  |

| 5          | MOSI        | SPI Master Out Slave In                             |  |

| 6          | RESET       | Reset signal to the device to be programmed         |  |

| 7          | MISO        | SPI Master In Slave Out                             |  |

| 8          | SCK         | SPI clock                                           |  |

| 9          |             | Not used                                            |  |

| 10         | GND         | Common ground                                       |  |

**Table 3** nRF ISP interface pin description

**Note:** RF\_VDD is used for signal level shifters on the Motherboard. Therefore, the power supply of the Motherboard does not have to match the power supply level of the connected application board. The application board must, however, be powered from its own power supply.

#### 2.11 nRF debug interface

A JTAG debug interface (**P12**) is available on the Motherboard to enable the nRFprobe hardware debugger to access nRF devices not found on a Development Kit module. This interface enables hardware debugging on your own application boards.

The nRF debug interface is wired in parallel with the nRF Module connectors MOD A (**P3**) and MOD B (**P4**). To use the nRF debug interface remove the Development Kit module from the Motherboard. *Figure 14* shows the pinout of the nRF debug interface. Please refer to the relevant nRF device product specification for debug interface pinout details.

Figure 14 nRF hardware debug interface pinout

| Pin number | Signal name | Description                                                                                                                                                              |

|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | TCK         | JTAG clock                                                                                                                                                               |

| 2          | GND         | Ground                                                                                                                                                                   |

| 3          | TDO         | JTAG data out                                                                                                                                                            |

| 4          | VEXT        | Application board supply voltage. Used by signal level shifters on the Motherboard to ensure correct signal levels between the Motherboard and target application board. |

| 5          | TMS         |                                                                                                                                                                          |

| 6          | VEXT        |                                                                                                                                                                          |

| 7          |             | Not used                                                                                                                                                                 |

| 8          | RESET       | nRF device reset                                                                                                                                                         |

| 9          | TDI         | JTAG data in                                                                                                                                                             |

| 10         |             | Not used                                                                                                                                                                 |

Table 4 nRF hardware debug interface pin description

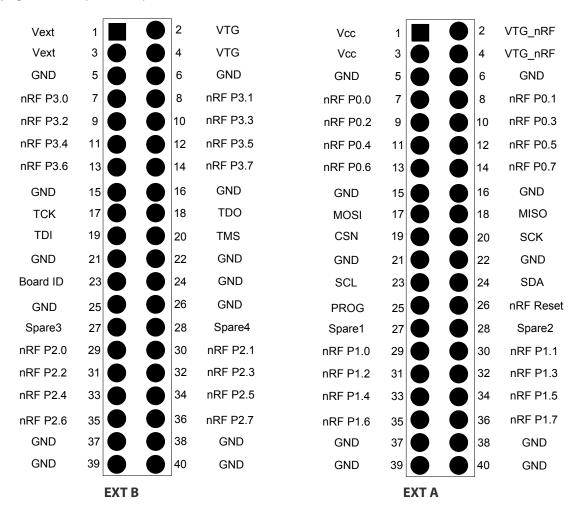

#### 2.12 Extension board connectors

The extension board connectors, EXT A (**P5**) and EXT B (**P6**), have the same pinout as the nRF module connectors, offering full access to all the I/Os of the Development Kit used.

The only exception is pin 23 on EXT B. This pin is used to identify the extension module. Please refer to *Table 1 on page 8* for the pin description.

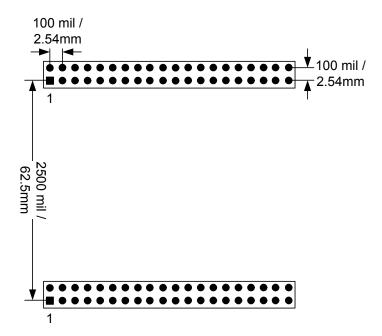

Figure 15 Extension board connectors - EXT B and EXT A

These connectors give you full access to all the nRF module I/O pins and the Motherboard power supply for application development. See *Figure 16 on page 18* for the mechanical dimensions of the extension board connectors.

**Figure 16** Mechanical dimensions of the extension board connectors

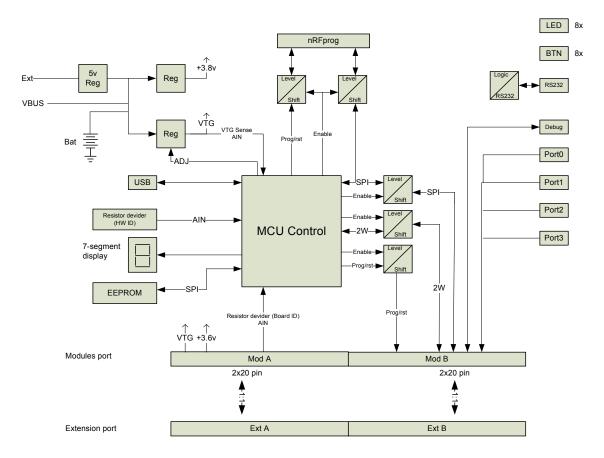

# 2.13 Block schematic

Figure 17 Motherboard (nRF6310) block schematic

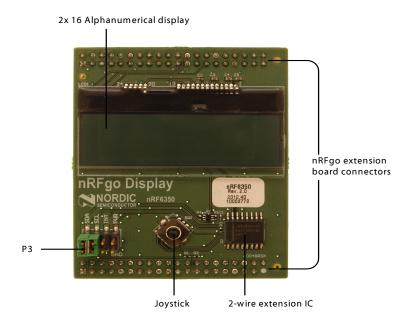

# 3 Display module (nRF6350)

Figure 18 Display module (nRF6350)

The nRF6350 extension board is equipped with an LCD and a four-way joystick with an input push button. Both the LCD and joystick are controlled with a 2-wire interface (SDA and SCL). The SDA and SLC signals are routed through the pin header **P3** to the extension board connector **P1**. See *Table 5* for a description. Place jumpers over pin 1-2 and pin 3-4 to guide these signals to **P1**.

| Pin Number | Signal Name | Description                                                                                                                                                                                                                                                     |

|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SDA'        | 2-wire data line, connected to the extension board connector P1, pin 24.                                                                                                                                                                                        |

| 2          | SDA         | 2-wire data line, connected to the onboard LCD and the joystick.                                                                                                                                                                                                |

| 3          | SCL'        | 2-wire clock line, connected to the extension board connector P1, pin 23.                                                                                                                                                                                       |

| 4          | SCL         | 2-wire clock line, connected to the onboard LCD and joystick.                                                                                                                                                                                                   |

| 5          | RESERVED    | Spare1 signal to the Motherboard MCU.                                                                                                                                                                                                                           |

| 6          | INT         | Interrupt signal from the I/O port expander controlling the joystick.                                                                                                                                                                                           |

| 7          | GND         | Common ground.                                                                                                                                                                                                                                                  |

| 8          | PWR         | Control signal for LCD and joystick power. Default on (HIGH) through onboard pull-up resistor. Display will be ON when the connection point is floating. The display/joystick can be set to OFF if you connect the PWR signal to an I/O line and set it to LOW. |

**Table 5** P3 pinout description

If you want to connect the SDA and SCL to alternative signal sources, remove the jumpers from **P3** and connect cables between pin 1-2 and pin 3-4 and the Motherboard port connectors instead. See *Figure 19*.

Figure 19 Alternative connection from the nRF6350 to the Motherboard

Please refer to the Software Development Kit (SDK) of your nRFgo compatible Development Kit for examples on how to use the display and joystick. Pinout for the extension board connectors can be found in *chapter 2.12 on page 17*.

## 3.1 Display description

The LCD is a 2x16 character alphanumeric LCD with a built-in 2-wire display controller. The display can be used by either the Motherboard MCU or by any nRFgo Development Kit module that has a 2-wire master. The LCD slave address is fixed to 0x3E, and cannot be changed. The built-in display controller is a ST7032i from Sitronix which supports standard HD44780 commands over the 2-wire serial interface.

**Note:** The LCD driver supply range is 3.0 V – 7.0 V, requiring that the LCD is operated at supply voltages higher than 3.0 V. For good contrast 3.3 V is recommended.

# 3.2 Joystick description

The joystick is connected to a 2-wire I/O port expander, MAX7329 from Maxim. The slave address of the I/O port expander is fixed to 0x3F. An interrupt output line signals when the joystick is being used. This interrupt line INT can be routed to SPARE1 through a jumper on **P3**, pin 5-6. (This was the default configuration for the previous version). The INT signal is an open collector output with pull-up to VDD (VDD = VEXT = nRF6350 supply voltage), meaning this signal can be used in an application by connecting a cable from INT pin on **P3** to one of the Motherboard port connectors.

# 4 Troubleshooting

I have connected the Motherboard to the PC with the USB cable, but the LEDs on the Motherboard don't light up.

- Verify that the Motherboard is turned ON (S9).

- Verify that the power selection button (**\$8**) is set to "VBUS".

- Remove all third party hardware connected to the Motherboard in order to remove possible short circuits.

- · Change USB port on your computer.

- Try a different USB cable.

# I have connected the Motherboard to an external power supply but the power indicator LEDs don't light up.

- Verify that the Motherboard is turned ON (S9).

- Verify that the power selection button (**\$8**) is set to "VSUPPLY".

- Remove all third party hardware connected to the Motherboard in order to remove possible short circuits.

- Make sure the external power supply level is within 8 20 V.

#### I can't see my Motherboard in the nRFgo Studio user interface.

- Verify that the USB connection is correct.

- · Verify that the Motherboard is switched ON. VCC and VTG LED should be lit.

- Make sure no other software is using the Motherboard. For example nRFprobe.

- Try a different USB port.

- Replace USB cable.

- · Restart nRFgo Studio.

- Remove and re-install USB drivers (or entire nRFgo Studio).

# My nRFgo Development Kit radio module won't fit into the nRF module socket on my nRFgo Motherboard (nRF6310 Rev. 1.4). What can I do?

In nRFgo Starter Kit revision 1.1 and higher versions, the nRFgo module socket connectors MOD A (P3) and MOD B (P4) on the nRFgo Motherboard are now of type Samtec TFC-120-02-L-D-A. You probably have an nRFgo radio module with Harwin M50-4322005 connectors which are not physically compatible with the Samtec TFC-120-02-L-D-A connectors on your new nRFgo Motherboard. You can easily make your nRFgo module fit into the nRF module socket of your nRFgo Motherboard by filing off the polarization pegs on each connector (marked with white circles in the following figure) on the nRFgo module.

**Figure 20** Polarization pegs for connectors on nRFgo module

## Liability disclaimer

Nordic Semiconductor ASA reserves the right to make changes without further notice to the product to improve reliability, function or design. Nordic Semiconductor ASA does not assume any liability arising out of the application or use of any product or circuits described herein.

## Life support applications

Nordic Semiconductor's products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Nordic Semiconductor ASA customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Nordic Semiconductor ASA for any damages resulting from such improper use or sale.

#### **Contact details**

For your nearest dealer, please see http://www.nordicsemi.com.

Information regarding product updates, downloads, and technical support can be accessed through your My Page account on our homepage.

Main office: Otto Nielsens veg 12

7052 Trondheim

Norway

Phone: +47 72 89 89 00 Fax: +47 72 89 89 89 Mailing address: Nordic Semiconductor

P.O. Box 2336 7004 Trondheim

Norway

## **Revision History**

| Date          | Version | Description                                                                                                                      |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------|

| October 2012  | 1.6     | Updated the document with the new template. Updated chapter 3 on page 20, Figure 1, Figure 2, Figure 5, Figure 18, and Figure 19 |

| August 2011   | 1.5     | Removed all references to the CD. Updated <i>Figure 1, Figure 2</i> , <i>Figure 3</i> , <i>Figure 5</i> , and <i>Figure 18</i> . |

| December 2010 | 1.4     | Updated chapter 4 on page 22.                                                                                                    |

| August 2009   | 1.3     | Updated <i>Table 3</i> .                                                                                                         |

| December 2008 | 1.2     | Updated <i>Figure 4</i> .                                                                                                        |