## DDR2 SDRAM FBDIMM

#### MT36HTS51272F - 4GB

For the latest data sheet, refer to Micron's Web site: www.micron.com

#### **Features**

- 240-pin DDR2 fully buffered, dual in-line memory module (FBDIMM) with ECC to detect and report channel errors to the host memory controller

- Fast data transfer rates: PC2-4200 and PC2-5300 using 533 MT/s and 667 MT/s DDR2 SDRAM components

- 3.2 Gb/s and 4.0 Gb/s link transfer rates

- High-speed, differential, point-to-point link between host memory controller and the AMB using serial, dual-simplex bit lanes

- 10-pair southbound (data path to FBDIMM)

- 14-pair northbound (data path from FBDIMM)

- Fault tolerant; can work around a bad bit lane in each direction

- High-density scaling with up to 8 dual-rank modules (288 DDR2 SDRAM devices) per channel

- SMBus interface to AMB for configuration register access

- In-band and out-of-band command access

- Deterministic protocol

- Enables memory controller to optimize DRAM accesses for maximum performance

- Delivers precise control and repeatable memory behavior

- Automatic DDR2 SDRAM bus and channel calibration

- Transmitter de-emphasis to reduce ISI

- MBIST and IBIST test functions

- Transparent mode for DDR2 SDRAM test support

- VDD = VDDQ = +1.8V for DDR2 SDRAM

- VREF = 0 .9V SDRAM C/A termination

- VCC = 1.5V for advanced memory buffer (AMB)

- VDDSPD = +1.7V to +3.6V for SPD EEPROM

- Serial presence-detect (SPD) with EEPROM

- · Gold edge contacts

- Dual rank

- Supports 95°C operation with 2X refresh (<sup>t</sup>REFI = 7.8µs at or below 85°C; <sup>t</sup>REFI = 3.9µs above 85°C)

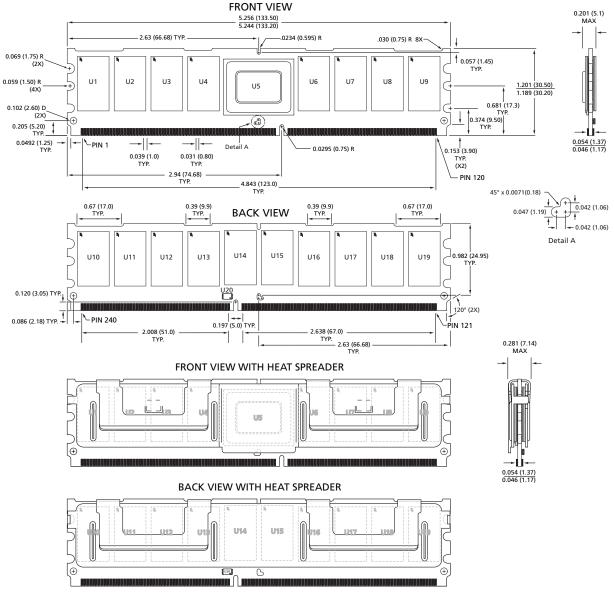

#### Figure 1: 240-Pin FBDIMM (MO-256 R/C J)

| Options                                        | Marking |

|------------------------------------------------|---------|

| • Package                                      |         |

| <ul> <li>240-pin FBDIMM (lead-free)</li> </ul> | Y       |

| • Frequency/CL <sup>1</sup>                    |         |

| -3.75ns @ CL = 5 (DDR2-667)                    | -667    |

| -3.75ns @ CL = 4 (DDR2-533)                    | -53E    |

| PCB height                                     |         |

| - 30.35mm (1.19in)                             |         |

Notes: 1. CL = CAS (READ) latency.

# 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Features

#### Table 1: FBDIMM/DDR2 SDRAM Addressing

| Parameter                 | 4GB                        |

|---------------------------|----------------------------|

| Refresh count             | 8K                         |

| Device bank addressing    | 8 (BA0, BA1, BA2)          |

| Device page size per bank | 1KB                        |

| Device configuration      | TwinDie™ 1Gb (256 Meg x 4) |

| Row addressing            | 16K (A0–A13)               |

| Column addressing         | 2K (A0-A9, A11)            |

| Module rank addressing    | 2 (\$0#, \$1#)             |

#### **Table 2: Performance Parameters**

| Speed Grade | Module Bandwidth | Peak Channel<br>Throughput | Link Transfer Rate | Latency<br>(CL- <sup>t</sup> RCD- <sup>t</sup> RP) |

|-------------|------------------|----------------------------|--------------------|----------------------------------------------------|

| -667        | PC2-5300         | 8.0 GB/s                   | 4.0 GT/s           | 5-5-5                                              |

| -53E        | PC2-4200         | 6.4 GB/s                   | 3.2 GT/s           | 4-4-4                                              |

### **Table 3: Part Numbers and Label Markings**

| Part Number <sup>1</sup> | Module Density | FBDIMM<br>Configuration | Label Key Attributes         |

|--------------------------|----------------|-------------------------|------------------------------|

| MT36HTS51272FY-53E       | 4GB            | 256 Meg x 72            | 4GB 2Rx4 PC2-4200J-444-10-C_ |

| MT36HTS51272FY-667       | 4GB            | 256 Meg x 72            | 4GB 2Rx4 PC2-5300J-555-10-C_ |

Notes: 1. All part numbers end with a two-place code (not shown), designating component and PCB revisions. Consult factory for current revision codes. Example: MT36HTS51272FY-53EC2.

## 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Table of Contents

## **Table of Contents**

| Features                                                        | 1   |

|-----------------------------------------------------------------|-----|

| Гable of Contents                                               | 3   |

| List of Figures                                                 | 4   |

| List of Tables                                                  | 5   |

| ntroductionntroduction                                          | 6   |

| FBDIMM Specification Details                                    | 6   |

| General Description                                             | 7   |

| Functional Description                                          | 9   |

| Advanced Memory Buffer (AMB)                                    | 9   |

| AMB Interface                                                   | .10 |

| High-Speed, Differential, Point-to-Point Link Interfaces (1.5V) | .10 |

| DDR2 Channel                                                    |     |

| SMBus Slave Interface                                           | .11 |

| Channel Latency                                                 | .11 |

| Peak Theoretical Throughput                                     | .11 |

| Hot-Add                                                         | .14 |

| Hot-Remove                                                      | .14 |

| Hot-Replace                                                     | .14 |

| FBDIMM Functional Block                                         | .15 |

| Pin Assignments and Descriptions                                | .16 |

| Electrical Specifications                                       | .19 |

| IDD Specifications and Conditions                               | .21 |

| Assumptions for All Parameters                                  | .21 |

| Differential Transmitter and Receiver Specifications            | .23 |

| AMB Initialization                                              |     |

| Serial Presence-Detect                                          | .28 |

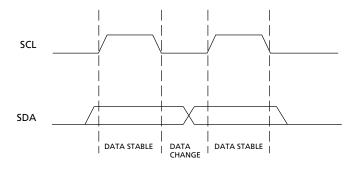

| SPD Clock and Data Conventions                                  | .28 |

| SPD Start Condition                                             | .28 |

| SPD Stop Condition                                              |     |

| SPD Acknowledge                                                 | .28 |

| Module Dimensions                                               | .35 |

## 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) List of Figures

## **List of Figures**

| Figure 1:  | 240-Pin FBDIMM (MO-256 R/C J)         | 1  |

|------------|---------------------------------------|----|

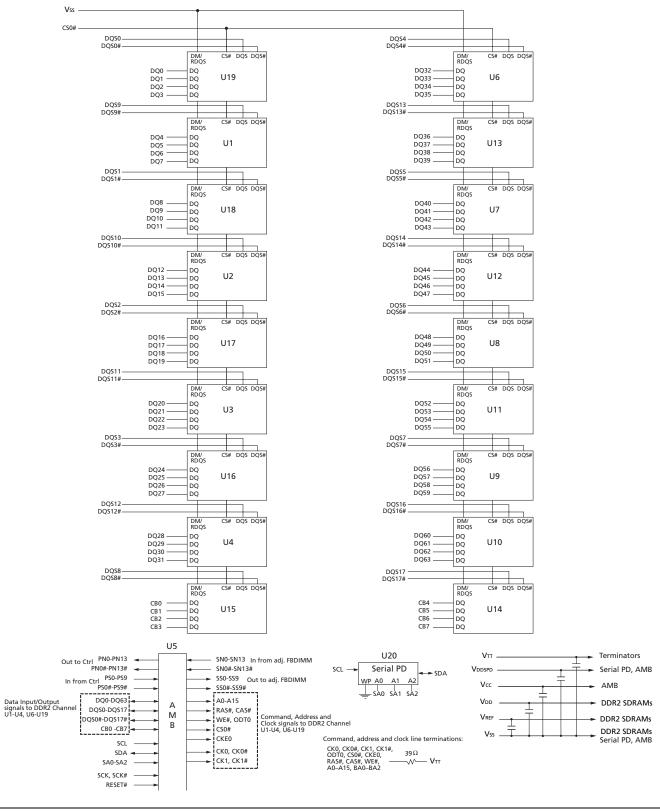

| Figure 2:  | FBDIMM System Block Diagram           |    |

| Figure 3:  | AMB Interface Block Diagram           | 10 |

| Figure 4:  | AMB Functional Block Diagram          |    |

| Figure 5:  | FBDIMM Functional Block Diagram       | 15 |

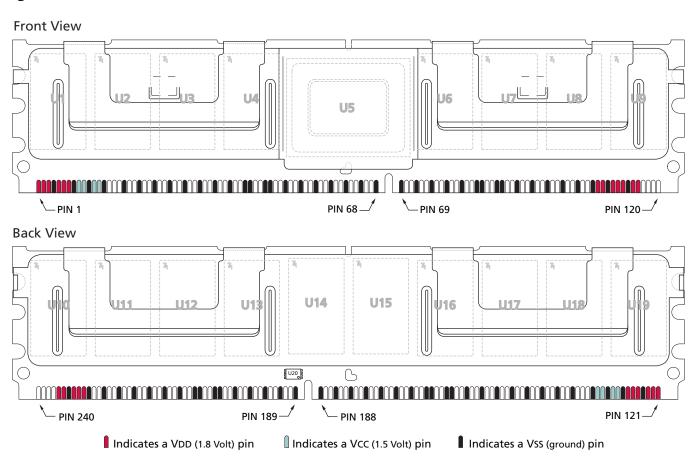

| Figure 6:  | FBDIMM Pin Locations                  |    |

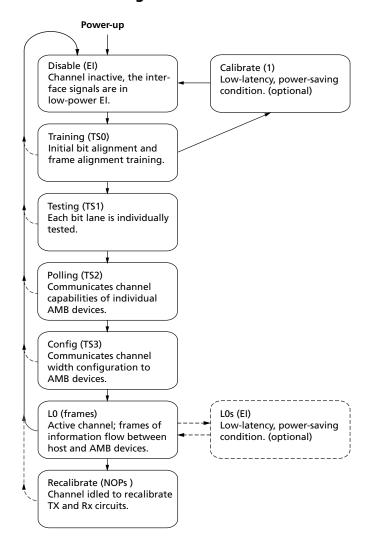

| Figure 7:  | AMB Initialization Flow Diagram       | 27 |

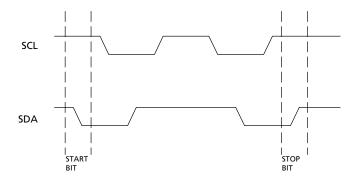

| Figure 9:  | Definition of Start and Stop          | 29 |

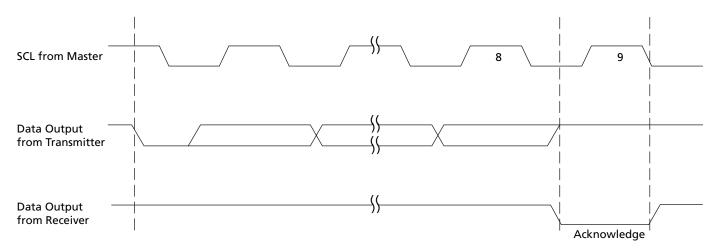

| Figure 10: | Acknowledge Response from Receiver    | 29 |

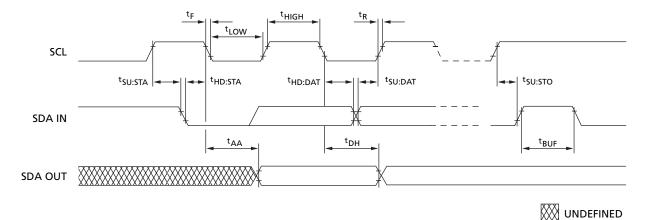

| Figure 11: | SPD EEPROM Timing Diagram             | 30 |

|            | 240-pin DDR2 FBDIMM Module Dimensions |    |

## 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) List of Tables

## **List of Tables**

| Table 1:  | FBDIMM/DDR2 SDRAM Addressing                          | 2  |

|-----------|-------------------------------------------------------|----|

| Table 2:  | Performance Parameters                                |    |

| Table 3:  | Part Numbers and Label Markings                       | 2  |

| Table 4:  | 240-pin FBDIMM Pin Assignment                         | 16 |

| Table 5:  | Pin Descriptions                                      |    |

| Table 6:  | Absolute Maximum Ratings                              | 19 |

| Table 7:  | Input DC Voltage and Operating Conditions             | 19 |

| Table 8:  | Timing Parameters                                     | 20 |

| Table 9:  | DDR2 IDD Specifications and Conditions – 4GB          | 21 |

| Table 10: | Reference Clock Input Specifications                  |    |

| Table 11: | Vtt Currents                                          |    |

| Table 12: | Differential Transmitter Output Specifications        | 23 |

| Table 13: | Differential Receiver Input Specifications            | 25 |

| Table 14: | EEPROM Device Select Code                             |    |

| Table 15: | EEPROM Operating Modes                                |    |

| Table 16: | Serial Presence-Detect EEPROM DC Operating Conditions |    |

| Table 17: | Serial Presence-Detect EEPROM AC Operating Conditions |    |

| Table 18: | MT36HTS51272F Serial Presence-Detect Matrix           |    |

## 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Introduction

### Introduction

### **FBDIMM Specification Details**

The JEDEC FBDIMM specification consists of the following sections and can be found at the JEDEC Web site member's area.

Each of these sections contains detailed information about the various aspects of FBDIMM construction, interfaces, and theory of operation. The JEDEC specification is simply too long and complex to condense into a single data sheet; minimal references are made throughout this document to give a brief overview. For design guidance and final specification information, designers must refer to the JEDEC FBDIMM specification.

#### 1. FBDIMM Design Specification

Defines the electrical and mechanical requirements for 240-pin, PC2-4200/PC2-5300, 72-bit wide, fully buffered double data rate synchronous DRAM dual in-line memory modules (DDR2 SDRAM FBDIMMs). These DDR2 SDRAM FBDIMMs are intended for use as main memory when installed in systems such as servers and workstations. PC2-4200/PC2-5300 refers to the DIMM naming convention in which PC2-4200/PC2-5300 indicates a 240-pin DDR2 DIMM running at 266/333 MHz DDR2 SDRAM clock speed and offering 4.2/5.3 GB/s bandwidth.

Reference design examples are included which provide an initial basis for FBDIMM designs. Modifications to these reference designs may be required to meet all system timing, signal integrity, and thermal requirements for PC2-4200/PC2-5300/ support. All FBDIMM implementations must use simulations and lab verification to ensure proper timing requirements and signal integrity in the design.

#### 2. FBDIMM Architecture and Protocol Specification

Describes FBDIMM channel topology, physical signaling, clocking, and data flow.

#### 3. FBDIMM AMB Specification

Core specification for a FBDIMM memory system. This document, along with the other core specifications, must be treated as a whole. Information critical to an AMB design appears in the other specifications, with specific cross-references provided.

#### 4. FBDIMM Link Signaling Specification

Defines the high-speed, differential, point-to-point signaling link for FBDIMM, operating at AMB VCC = 1.5V, provided at the FBDIMM connector. This specification also applies to FBDIMM host chips which may operate with a different supply voltage. The link consists of a transmitter, a receiver, and the interconnect between them. The transmitter sends serialized bits into a lane and the receiver accepts the electrical signals of the serialized bits and transforms them into a serialized bit-stream. The first-generation FBDIMM link is specified for  $3.2-4.0~{\rm Gb/s}$  and defined for three distinct bit rates:  $3.2~{\rm Gb/s}$  and  $4.0~{\rm Gb/s}$ .

The link utilizes a derived-clock approach and transmitter de-emphasis to compensate for channel loss characteristics. The link definition has the flexibility to accommodate future silicon enhancement circuits, such as forwarded clocking or advanced equalization techniques, to meet future signaling targets.

#### 5. FBDIMM DFx Specification

Defines design for test, design for manufacturing, and design for validation (DFx) requirements and implementation guidelines for FBDIMM technology.

#### 6. FBDIMM SPD Specification

This section describes the serial presence-detect (SPD) values for FBDIMMs, referenced in the SPD "Specific Features" standard document. The SPD fields indicated in this specification will occur in the order presented in section 1.1 of the JEDEC document. (Note that the descriptions of bytes 0 and 1 differ from those in previous SPD standards.) Further description of byte 2 is found in Appendix A of the JEDEC FBDIMM SPD standard. All unused entries will be coded as 0x00. All unused bits in defined bytes will be coded as 0, except where noted.

## **General Description**

The Micron FBDIMM adheres to the currently proposed industry specifications for FBDIMMs. This data sheet represents a minimal subset of the FBDIMM and AMB specification details and will be revised further as the specification matures and is approved and released. This document is to be used only as an introduction to the industry specification, which will serve as the final reference for any an all design parameters and criteria.

Micron's FBDIMM is a high-bandwidth, large-capacity-channel solution that has a narrow host interface. FBDIMMs use DDR2 SDRAM devices isolated from the channel behind a buffer on the FBDIMM. Memory-device capacity remains high and total memory capacity scales with DDR2 SDRAM bit density.

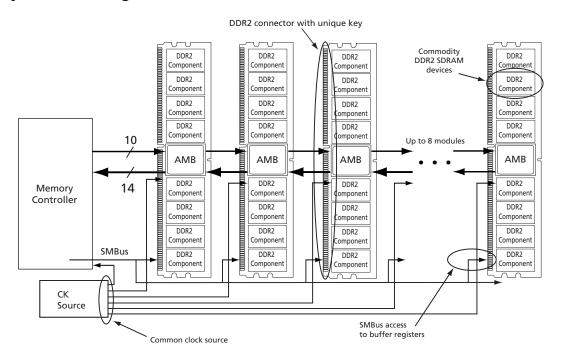

As shown in Figure 2 on page 8, the FBDIMM channel provides a communication path from a host controller to an array of DDR2 SDRAM devices, with the DDR2 SDRAM devices buffered behind an AMB device. The physical isolation of the DDR2 SDRAM devices from the channel enables the flexibility to enhance the communication path to significantly increase reliability and availability of the memory subsystem.

Micron's FBDIMM features a novel architecture, including the AMB that isolates the DDR2 SDRAM devices from the channel. This single-chip AMB component, located in the center of each FBDIMM, acts as a repeater and buffer for all signals and commands exchanged between the host controller and DDR2 SDRAM devices, including data input and output. The AMB communicates with the host controller and adjacent FBDIMMs on a system board using an industry-standard, high-speed, differential, point-to-point interface at 1.5V.

The AMB also allows buffering of memory traffic to support large memory capacities. All memory control for the DDR2 SDRAM devices resides in the host, including memory request initiation, timing, refresh, scrubbing, sparing, configuration access, and power management. The AMB interface is responsible for handling channel and memory requests to and from the local FBDIMM and for forwarding requests to other FBDIMMs on the memory channel.

Figure 2: FBDIMM System Block Diagram

## **Functional Description**

### **Advanced Memory Buffer (AMB)**

The AMB reference design complies with the JEDEC standard, "FBDIMM Architecture and Protocol Specification." It is expected that there will be AMB multiple vendors, which will offer at least the minimum functionality set forth in the industry specification. To achieve optimal operation and compatibility with DDR2 SDRAM device and host/controller offerings, each vendor's AMB will have a unique set of personality bytes contained in the SPD for setting up and fine tuning that device.

The FBDIMM specification defines a number of options to support the requirements of different applications. The capabilities of the AMB are communicated to the host during the initialization process in the TS2 training pattern and in bits readable in the features register in the AMB.

The AMB is responsible for handling FBDIMM channel and memory requests to and from the local FBDIMM and for forwarding requests to other FBDIMMs on the channel. A complete and detailed description of the AMB is contained in the proposed FBDIMM AMB Specification. The AMB is a memory interface that connects an array of DDR2 SDRAM devices to the FBDIMM channel. The AMB is a slave device on the channel responding to channel commands and forwarding channel commands to other AMB devices.

All memory control for the DDR2 SDRAM resides in the host, including memory request initiation, timing, refresh, scrubbing, sparing, configuration access, and power management

The AMB is expected to perform the following functions:

- Support channel initialization procedures as defined in the initialization chapter of the FBDIMM Architecture and Protocol Specification to align the clocks and the frame boundaries and verify channel connectivity

- Support the forwarding of southbound and northbound frames, servicing requests directed to a specific FBDIMM's AMB, as defined in the protocol chapter of the specification, and merging the return data into the northbound frames

- Initialize northbound frames if the FBDIMM's AMB is the last, southern-most frame on the channel

- Detect errors on the channel and report them to the host memory controller

- Support the FBDIMM configuration register set as defined in the FBDIMM AMB specification register chapter of the specification

- Act as a DRAM memory buffer for all read, write, and configuration accesses addressed to a specific FBDIMM's AMB

- Provide a read and write buffer FIFO

- Support an SMBus protocol interface for access to the AMB configuration registers

- Provide features to support MEMBIST and IBIST test functions

- Provide a register interface for the thermal sensor and status indicator

- Function as a repeater to extend the maximum length of FBDIMM Links

- Reconfigure FBDIMM inputs from differential high-speed link receivers to two single-ended, low-speed receivers (~200 MHz). These inputs directly control DDR2 command/address and input data that replicates to all DDR2 SDRAM devices.

- Bypass high speed parallel/serial circuitry and provide test results back to the tester, using low-speed FBDIMM outputs.

#### **AMB Interface**

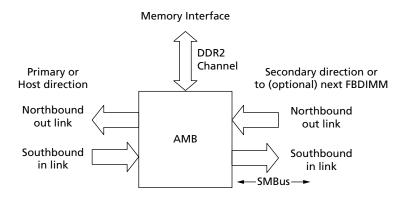

Figure 3 illustrates the AMB and all of its interfaces. They consist of two FBDIMM links, one DDR2 channel, and an SMBus interface. Each FBDIMM link connects the AMB to a host memory controller or an adjacent FBDIMM. The DDR2 channel supports direct connection to the DDR2 SDRAMs on an FBDIMM.

The FBDIMM channel uses a daisy-chain topology to provide expansion from a single FBDIMM per channel to up to eight FBDIMMs per channel. The host sends data on the southbound link to the first FBDIMM, where it is received and redriven to the second FBDIMM. On the southbound data path, each FBDIMM receives the data and redrives the data to the next FBDIMM, until the last FBDIMM receives the data. The last FBDIMM in the chain initiates the transmission of northbound data in the direction of the host. On the northbound data path, each FBDIMM receives the data and redrives the data to the next FBDIMM until the host is reached.

Figure 3: AMB Interface Block Diagram

### High-Speed, Differential, Point-to-Point Link Interfaces (1.5V)

The AMB supports one FBDIMM channel consisting of two bidirectional link interfaces using high-speed differential point-to-point electrical signaling. The southbound input link is 10 lanes wide. It carries commands and write data from the host memory controller, or the adjacent FBDIMM in the host direction, to the next FBDIMM in the chain.

The northbound input link is 14 lanes wide. It carries read return data or status information from one FBDIMM to the next in the host direction and multiplexes in any internally generated READ return data or status information.

Data and commands sent to the DDR2 SDRAM devices travel southbound on 10 primary differential signal line pairs. Data and status information received from the DDR2 SDRAM devices travel northbound on 14 primary differential pairs. Data and commands sent to the upstream adjacent FBDIMM are repeated and travel further southbound on 10 secondary differential pairs. Data and status information received from the upstream adjacent FBDIMM travel further northbound on 14 secondary differential pairs.

#### **DDR2 Channel**

The AMB DDR2 channel supports direct connection to DDR2 SDRAM devices. The DDR2 channel supports two ranks of eight banks with 16 row/column-request, 64 data, and eight check-bit signals. There are two copies of address and command signals to support FBDIMM routing and electrical requirements. Four transfer bursts are driven on the data and check-bit lines at 800 MHz.

Propagation delays can differ between read data/check-bit strobe lanes on a given channel. Each strobe can be calibrated by hardware-state machines using WRITE/READ trial and error. Hardware aligns the read data and check-bits to a single core clock. The AMB provides four copies of the command clock phase references (CK[3:0]) and write data/check-bit strobes (DQS) for each DDR2 SDRAM device nibble.

#### **SMBus Slave Interface**

AMB support for an SMBus interface allows system access to configuration registers independent of the FBDIMM link. The AMB will never be a master on the SMBus, only a slave. Serial SMBus data transfer is supported at 100 KHz. SMBus access to the AMB may be a requirement to boot and to set link strength, frequency, and other parameters needed to ensure robust configurations. It is also required for diagnostic support when the high-speed link is down. The SMBus address straps located on the FBDIMM connector are used to set the unique ID.

### **Channel Latency**

FBDIMM channel latency is measured from the time a read request is driven on the FBDIMM channel pins to the time when the first 16 bytes (second chunk) of read completion data is sampled by the memory controller.

When not using variable READ latency, the latency for a specific FBDIMM on a channel is always equal to the latency for any other FBDIMM on that channel. However, the latency for each FBDIMM in a specific configuration with some number of FBDIMMs installed may not be equal to the latency for each FBDIMM in a configuration with some different number of FBDIMMs installed. As more FBDIMMs are added to the channel, additional latency is required to read from each FBDIMM on the channel.

Because the channel is based on point-to-point interconnection of buffer components between FBDIMMs, memory requests are required to travel through N - 1 buffers before reaching the Nth buffer. The result is that a four-FBDIMM channel configuration will have greater idle READ latency than a one-FBDIMM channel configuration.

The variable READ latency capability can be used to reduce latency for FBDIMMs closer to the host. The idle latencies listed in this section are representative of what might be achieved in typical AMB designs. Actual implementations with latencies less than the values listed will have higher application performance and vice versa.

### **Peak Theoretical Throughput**

An FBDIMM channel transfers read completion data on the northbound data connection; 144 bits of data are transferred for every northbound data frame. This matches the 18-byte data transfer of an ECC DDR2 SDRAM device in a single DDR2 SDRAM command clock. A DDR2 SDRAM device burst of eight from a single channel, or burst of four from two lock-step channels, provides a total of 72 bytes of data (64 bytes plus 8 bytes ECC). The AMB frame rate matches the DDR2 SDRAM command clock because of the fixed 6:1 ratio of the FBDIMM channel clock to the DDR2 SDRAM command clock.

Therefore, the northbound data connection will exhibit the same peak theoretical throughput as a single DDR2 SDRAM channel. For example, when using DDR2-533 components, the peak theoretical bandwidth of the northbound data connection is 4.267 GB/s.

Write data is transferred on the southbound command and data connection, via Command + Wdata frames; 72 bits of data are transferred per frame. Two Command + Wdata frames match the 18-byte data transfer of an ECC DDR2 SDRAM in a single DDR2 SDRAM command clock.

A DDR2 SDRAM burst of eight transfers from a single channel, or a burst of four from two lock-step channels, provides a total of 72 bytes of data (64 bytes plus 8 bytes ECC). When the FBDIMM frame rate matches the DDR2 SDRAM command clock, the south-bound command and data connection will exhibit one-half the peak theoretical throughput of a single DDR2 SDRAM channel. For example, when using DDR2-533 SDRAMs, the peak theoretical bandwidth of the southbound command and data connection is 2.133 GB/s.

The total peak theoretical throughput for a single FBDIMM channel is defined as the sum of the peak theoretical throughput of the northbound data connection and the southbound command and data connection. When the FBDIMM frame rate matches the DDR2 SDRAM command clock, it equals 1.5X the peak theoretical throughput of a single DDR2 SDRAM channel. For example, when using DDR2-533 SDRAM devices, the peak theoretical throughput of a DDR2-533 channel would be 4.267 GB/s, while the peak theoretical throughput of an FBDIMM-533 channel would be 6.4 GB/s.

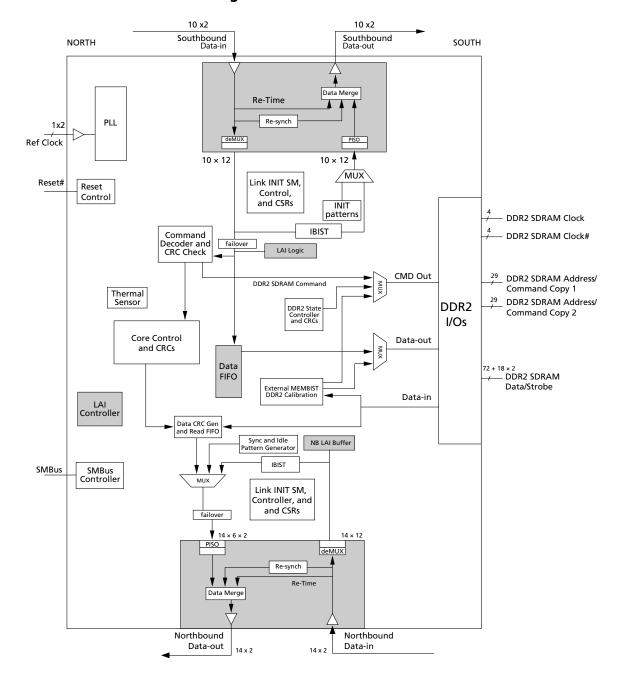

Figure 4: AMB Functional Block Diagram

#### **Hot-Add**

The FBDIMM channel does not provide a mechanism to automatically detect and report the addition of a new FBDIMM south of the currently active last FBDIMM. It is assumed the system will be notified through some means of the addition of one or more new FBDIMMs so that specific commands can be sent to the host controller to initialize the newly added FBDIMM(s) and perform a hot-add reset to bring them into the channel timing domain. It should be noted that the power to the FBDIMM socket must be removed before a hot-add FBDIMM is inserted or removed. Applying or removing the power to a FBDIMM socket is a system platform function.

#### **Hot-Remove**

To remove one or more FBDIMMs, the host must perform a fast reset sequence targeted at the last FBDIMM that will be retained on the channel. The fast reset re-establishes the appropriate last FBDIMM so that the southbound transmission outputs of the last active FBDIMM and the southbound and northbound outputs of the FBDIMMs beyond the last active FBDIMM are disabled. Once the appropriate outputs are disabled, the system can coordinate the procedure to remove power in preparation for physical removal of the FBDIMM. Note that the power to the FBDIMM socket must be removed before a hot-remove FBDIMM is inserted or removed. Applying or removing the power to a FBDIMM socket is a system platform function.

### **Hot-Replace**

Hot-replace of FBDIMMs is accomplished by combining the hot-remove and hot-add processes.

#### 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) FBDIMM Functional Block

### **FBDIMM Functional Block**

Figure 5: FBDIMM Functional Block Diagram

### 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Pin Assignments and Descriptions

## **Pin Assignments and Descriptions**

Table 4: 240-pin FBDIMM Pin Assignment

| Pin | Front            | Pin | Back             | Pin | Front | Pin | Back             | Pin | Front            | Pin | Back             | Pin | Front            | Pin | Back             |

|-----|------------------|-----|------------------|-----|-------|-----|------------------|-----|------------------|-----|------------------|-----|------------------|-----|------------------|

| 1   | Vdd              | 121 | Vdd              | 31  | PN3   | 151 | SN3              | 61  | PN9#             | 181 | SN9#             | 91  | PS9#             | 211 | SS9#             |

| 2   | Vdd              | 122 | Vdd              | 32  | PN3#  | 152 | SN3#             | 62  | Vss              | 182 | Vss              | 92  | Vss              | 212 | Vss              |

| 3   | Vdd              | 123 | Vdd              | 33  | Vss   | 153 | Vss              | 63  | PN10             | 183 | SN10             | 93  | PS5              | 213 | SS5              |

| 4   | Vss              | 124 | Vss              | 34  | PN4   | 154 | SN4              | 64  | PN10#            | 184 | SN10#            | 94  | PS5#             | 214 | SS5#             |

| 5   | Vdd              | 125 | Vdd              | 35  | PN4#  | 155 | SN4#             | 65  | Vss              | 185 | Vss              | 95  | Vss              | 215 | Vss              |

| 6   | Vdd              | 126 | Vdd              | 36  | Vss   | 156 | Vss              | 66  | PN11             | 186 | SN11             | 96  | PS6              | 216 | SS6              |

| 7   | Vdd              | 127 | Vdd              | 37  | PN5   | 157 | SN5              | 67  | PN11#            | 187 | SN11#            | 97  | PS6#             | 217 | SS6#             |

| 8   | Vss              | 128 | Vss              | 38  | PN5#  | 158 | SN5#             | 68  | Vss              | 188 | Vss              | 98  | Vss              | 218 | Vss              |

| 9   | Vcc              | 129 | Vcc              | 39  | Vss   | 159 | Vss              | 69  | Vss              | 189 | Vss              | 99  | PS7              | 219 | SS7              |

| 10  | Vcc              | 130 | Vcc              | 40  | PN13  | 160 | SN13             | 70  | PS0              | 190 | SS0              | 100 | PS7#             | 220 | SS7#             |

| 11  | Vss              | 131 | Vss              | 41  | PN13# | 161 | SN13#            | 71  | PSO#             | 191 | SSO#             | 101 | Vss              | 221 | Vss              |

| 12  | Vcc              | 132 | Vcc              | 42  | Vss   | 162 | Vss              | 72  | Vss              | 192 | Vss              | 102 | PS8              | 222 | SS8              |

| 13  | Vcc              | 133 | Vcc              | 43  | Vss   | 163 | Vss              | 73  | PS1              | 193 | SS1              | 103 | PS8#             | 223 | SS8#             |

| 14  | Vss              | 134 | Vss              | 44  | RFU   | 164 | RFU <sup>1</sup> | 74  | PS1#             | 194 | SS1#             | 104 | Vss              | 224 | Vss              |

| 15  | Vπ               | 135 | VTT              | 45  | RFU   | 165 | RFU <sup>1</sup> | 75  | Vss              | 195 | Vss              | 105 | RFU <sup>2</sup> | 225 | RFU <sup>2</sup> |

| 16  | VID1             | 136 | VID0             | 46  | Vss   | 166 | Vss              | 76  | PS2              | 196 | SS2              | 106 | RFU <sup>2</sup> | 226 | RFU <sup>2</sup> |

| 17  | RESET#           | 137 | DNU/M_Test       | 47  | Vss   | 167 | Vss              | 77  | PS2#             | 197 | SS2#             | 107 | Vss              | 227 | Vss              |

| 18  | Vss              | 138 | Vss              | 48  | PN12  | 168 | SN12             | 78  | Vss              | 198 | Vss              | 108 | Vdd              | 228 | SCK              |

| 19  | RFU <sup>2</sup> | 139 | RFU <sup>2</sup> | 49  | PN12# | 169 | SN12#            | 79  | PS3              | 199 | SS3              | 109 | VDD              | 229 | SCK#             |

| 20  | RFU <sup>2</sup> | 140 | RFU <sup>2</sup> | 50  | Vss   | 170 | Vss              | 80  | PS3#             | 200 | SS3#             | 110 | Vss              | 230 | Vss              |

| 21  | Vss              | 141 | Vss              | 51  | PN6   | 171 | SN6              | 81  | Vss              | 201 | Vss              | 111 | Vdd              | 231 | Vdd              |

| 22  | PN0              | 142 | SN0              | 52  | PN6#  | 172 | SN6#             | 82  | PS4              | 202 | SS4              | 112 | Vdd              | 232 | VDD              |

| 23  | PN0#             | 143 | SNO#             | 53  | Vss   | 173 | Vss              | 83  | PS4#             | 203 | SS4#             | 113 | Vdd              | 233 | Vdd              |

| 24  | Vss              | 144 | Vss              | 54  | PN7   | 174 | SN7              | 84  | Vss              | 204 | Vss              | 114 | Vss              | 234 | Vss              |

| 25  | PN1              | 145 | SN1              | 55  | PN7#  | 175 | SN7#             | 85  | Vss              | 205 | Vss              | 115 | Vdd              | 235 | VDD              |

| 26  | PN1#             | 146 | SN1#             | 56  | Vss   | 176 | Vss              | 86  | RFU <sup>1</sup> | 206 | RFU <sup>1</sup> | 116 | VDD              | 236 | VDD              |

| 27  | Vss              | 147 | Vss              | 57  | PN8   | 177 | SN8              | 87  | RFU <sup>1</sup> | 207 | RFU <sup>1</sup> | 117 | VTT              | 237 | VTT              |

| 28  | PN2              | 148 | SN2              | 58  | PN8#  | 178 | SN8#             | 88  | Vss              | 208 | Vss              | 118 | SA2              | 238 | VDDSPD           |

| 29  | PN2#             | 149 | SN2#             | 59  | Vss   | 179 | Vss              | 89  | Vss              | 209 | Vss              | 119 | SDA              | 239 | SA0              |

| 30  | Vss              | 150 | Vss              | 60  | PN9   | 180 | SN9              | 90  | PS9              | 210 | SS9              | 120 | SCL              | 240 | SA1              |

- Notes: 1. Reserved for forwarded clocks to be used in future module implementations.

- 2. Reserved for future architecture flexibility.

- 3. The following signals are CRC bits and thus appear out of the normal sequence: PN12/ PN12#, SN12/SN12#, PN13/PN13#, SN13/SN13#, PS9/PS9#, SS9/SS9#.

- 4. RFU = reserved for future use.

## 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Pin Assignments and Descriptions

Figure 6: FBDIMM Pin Locations

## 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Pin Assignments and Descriptions

**Table 5: Pin Descriptions**

|                                                                                                                                                                                                                                                                                                                                                                           |                | _      |                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Numbers                                                                                                                                                                                                                                                                                                                                                               | Symbol         | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                         |

| 228                                                                                                                                                                                                                                                                                                                                                                       | SCK            | Input  | System clock input, positive line                                                                                                                                                                                                                                                                                                                                                   |

| 229                                                                                                                                                                                                                                                                                                                                                                       | SCK#           | Input  | System clock Input, negative line                                                                                                                                                                                                                                                                                                                                                   |

| 22, 25, 28, 31, 34, 37, 40, 48, 51, 54, 57, 60, 63, 66                                                                                                                                                                                                                                                                                                                    | PN[13:0]       | Output | Primary northbound data, positive lines                                                                                                                                                                                                                                                                                                                                             |

| 23, 26, 29, 32, 35, 38, 41, 49, 52, 55, 58, 61, 64, 67                                                                                                                                                                                                                                                                                                                    | PN#[13:0]      | Output | Primary northbound data, negative lines                                                                                                                                                                                                                                                                                                                                             |

| 70, 73, 76, 79, 82, 90, 93, 96, 99, 102                                                                                                                                                                                                                                                                                                                                   | PS[9:0]        | Input  | Primary southbound data, positive lines                                                                                                                                                                                                                                                                                                                                             |

| 71, 74, 77, 80, 83, 91, 94, 97, 100,<br>103                                                                                                                                                                                                                                                                                                                               | PS#[9:0]       | Input  | Primary southbound data, negative lines                                                                                                                                                                                                                                                                                                                                             |

| 142, 145, 148, 151, 154, 157, 160, 168, 171, 174, 177, 180, 183, 186                                                                                                                                                                                                                                                                                                      | SN[13:0]       | Output | Secondary northbound data, positive lines                                                                                                                                                                                                                                                                                                                                           |

| 143, 146, 149, 152, 155, 158, 161, 169, 172, 175, 178, 181, 184, 187                                                                                                                                                                                                                                                                                                      | SN#[13:0]      | Output | Secondary northbound data, negative lines                                                                                                                                                                                                                                                                                                                                           |

| 190, 193, 196, 199, 202, 210, 213, 216, 219, 222                                                                                                                                                                                                                                                                                                                          | SS[9:0]        | Input  | Secondary southbound data, positive lines                                                                                                                                                                                                                                                                                                                                           |

| 191, 194, 197, 200, 203, 211, 214, 217, 220, 223                                                                                                                                                                                                                                                                                                                          | SS#[9:0]       | Input  | Secondary southbound data, negative lines                                                                                                                                                                                                                                                                                                                                           |

| 120                                                                                                                                                                                                                                                                                                                                                                       | SCL            | Input  | Serial presence detect (SPD) clock input                                                                                                                                                                                                                                                                                                                                            |

| 119                                                                                                                                                                                                                                                                                                                                                                       | SDA            | I/O    | SPD data input / output                                                                                                                                                                                                                                                                                                                                                             |

| 118, 239, 240                                                                                                                                                                                                                                                                                                                                                             | SA[2:0]        | I/O    | SPD address inputs, also used to select the FBDIMM number in the AMB                                                                                                                                                                                                                                                                                                                |

| 16, 136                                                                                                                                                                                                                                                                                                                                                                   | VID[1:0]       | NC     | Voltage ID: These pins must be unconnected for DDR2-based FBDIMMs; VID[0] is VDD value: OPEN = 1.8V, GND = 1.5V; VID[1] is VCC value: OPEN = 1.5V, GND = 1.2V                                                                                                                                                                                                                       |

| 17                                                                                                                                                                                                                                                                                                                                                                        | RESET#         | Supply | AMB reset signal                                                                                                                                                                                                                                                                                                                                                                    |

| 9, 10, 12, 13, 129, 130, 132, 133                                                                                                                                                                                                                                                                                                                                         | Vcc            | Supply | AMB core power and AMB channel interface power (1.5V)                                                                                                                                                                                                                                                                                                                               |

| 1, 2, 3, 5, 6, 7, 108, 109, 111, 112, 113, 115, 116, 121, 122, 123, 125, 126, 127, 231, 232, 233, 235, 236                                                                                                                                                                                                                                                                | VDD            | Supply | DRAM power and AMB DRAM I/O power (1.8V)                                                                                                                                                                                                                                                                                                                                            |

| 15, 117, 135, 237                                                                                                                                                                                                                                                                                                                                                         | VTT            | Supply | DRAM address/command/clock termination power (VDD/2)                                                                                                                                                                                                                                                                                                                                |

| 238                                                                                                                                                                                                                                                                                                                                                                       | VDDSPD         | Supply | SPD power                                                                                                                                                                                                                                                                                                                                                                           |

| 4, 8, 11, 14, 18, 21, 24, 27, 30, 33, 36, 39, 42, 43, 46, 47, 50, 53, 56, 59, 62, 65, 68, 69, 72, 75, 78, 81, 84, 85, 88, 89, 92, 95, 98, 101, 104, 107, 110, 114, 124, 128, 131, 134, 138, 141, 144, 147, 150, 153, 156, 159, 162, 163, 166, 167, 170, 173, 176, 179, 182, 185, 188, 189, 192, 195, 198, 201, 204, 205, 208, 209, 212, 215, 218, 221, 224, 227, 230, 234 | Vss            | Supply | Ground                                                                                                                                                                                                                                                                                                                                                                              |

| 19, 20, 44, 45, 86, 87, 105, 106, 139, 140, 164, 165, 206, 207, 225, 226                                                                                                                                                                                                                                                                                                  | RFU            | RFU    | Reserved for future use                                                                                                                                                                                                                                                                                                                                                             |

| 137                                                                                                                                                                                                                                                                                                                                                                       | DNU/<br>M_Test | DNU    | The DNU/M_Test pin provides an external connection on R/Cs A—D for testing the margin of VREF, which is produced by a voltage divider on the module. It is not intended to be used in normal system operation and must not be be connected (DNU) in a system. This test pin may have other features on future card designs and will be included in this specification at that time. |

# 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Electrical Specifications

## **Electrical Specifications**

Stresses greater than those listed in Table 6 may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may adversely affect reliability.

**Table 6: Absolute Maximum Ratings**

| Parameter                                         | Symbol            | Min  | Max  | Units | Notes |

|---------------------------------------------------|-------------------|------|------|-------|-------|

| Voltage on any pin relative to Vss                | VIN, VOUT         | -0.3 | 1.75 | V     |       |

| Voltage on Vcc pin relative to Vss                | Vcc               | -0.3 | 1.75 | V     |       |

| Voltage on VDD pin relative to Vss                | VDD               | -0.5 | 2.3  | V     |       |

| Voltage on VTT pin relative to Vss                | VTT               | -0.5 | 2.3  | V     |       |

| Storage temperature                               | T <sub>STG</sub>  | -55  | 100  | °C    |       |

| DDR2 SDRAM device operating temperature (ambient) | T <sub>CASE</sub> | 0    | 95   | °C    | 1, 2  |

| AMB device operating temperature (ambient)        |                   | 0    | 110  | °C    |       |

Notes:

- T<sub>CASE</sub> is specified at 95°C only when using 2X refresh timing (<sup>t</sup>REFI = 7.8µs at or below 85°C; <sup>t</sup>REFI = 3.9µs above 85°C);DDR2 SDRAM component datasheet, though the FBDIMM does not have an IT option.

- 2. See applicable DDR2 SDRAM component datasheet for <sup>t</sup>REFI and extended mode register settings. The <sup>t</sup>REFI<sub>IT</sub> parameter is used to specify the doubled refresh interval necessary to sustain 95°C operation; however, the FBDIMM does not have an IT option.

**Table 7: Input DC Voltage and Operating Conditions**

| Parameter                          | Symbol  | Min        | Nom        | Мах        | Units | Notes |

|------------------------------------|---------|------------|------------|------------|-------|-------|

| AMB supply voltage                 | Vcc     | 1.46       | 1.50       | 1.54       | V     | _     |

| DDR2 SDRAM supply voltage          | VDD     | 1.7        | 1.8        | 1.9        | V     | _     |

| Termination voltage                | VTT     | 0.48 × VDD | 0.50 × VDD | 0.52 × VDD | V     | -     |

| EEPROM supply voltage              | VDDSPD  | 1.7        | -          | 3.6        | V     | -     |

| SPD Input HIGH (logic 1) voltage   | VIH(DC) | 2.1        | -          | VDDSPD     | V     | 1     |

| SPD Input LOW (logic 0) voltage    | VIL(DC) |            | -          | 0.8        | V     | 1     |

| RESET Input HIGH (logic 1) voltage | Vih(DC) | 1.0        | -          |            | V     | 2     |

| RESET Input LOW (logic 0) voltage  | VIL(DC) |            | -          | 0.5        | V     | 1     |

| Leakage Current (RESET)            | lL      | -90        | -          | 90         | μΑ    | 2     |

| Leakage Current (link)             | lL      | -5         | _          | 5          | μΑ    | 3     |

Notes:

- 1. Applies to SMB and SPD bus signals.

- 2. Applies to AMB CMOS signal RESET#.

- 3. For all other AMB related DC parameters, please refer to the high-speed differential link interface specification.

# 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Electrical Specifications

**Table 8: Timing Parameters**

| Parameter                                             | Symbol                    | Min | Тур   | Max     | Units  | Notes |

|-------------------------------------------------------|---------------------------|-----|-------|---------|--------|-------|

| Electrical idle (EI) assertion pass-through timing    | <sup>t</sup> El Propagate | _   | _     | 4       | CK     |       |

| El de-assertion pass-through timing                   | <sup>t</sup> EID          | _   | _     | Bitlock | CK     | 2     |

| El assertion duration                                 | <sup>t</sup> EI           | 100 | _     | _       | CK     | 1, 2  |

| FBDIMM command to DDR@ clock out that latches command | -                         | -   | 8.1   | _       | ns     | 3     |

| FBDIMM command to DDR2 WRITE                          | _                         | _   | TBD   | _       | ns     |       |

| DDR2 READ to FBDIMM (last FBDIMM)                     | _                         | _   | 5.0   | _       | ns     | 4     |

| Resample pass-through time                            | _                         | _   | 1.075 | _       | ns     |       |

| Resynch pass-through time                             | _                         | _   | 2.075 | _       | ns     |       |

| Bitlock interval                                      | <sup>t</sup> Bitlock      | _   | _     | 119     | frames | 1     |

| Framelock interval                                    | <sup>t</sup> Framelock    | _   | _     | 154     | frames | 1     |

Notes:

- 1. Defined in FBDIMM architecture and protocol specification.

- 2. Clocks defined as core clocks 2 × SCK input.

- 3. For DDR2-667 (PC2-5300), this is measured from the beginning of the frame at the south-bound input to the DDR2 clock output that latches the first command of a frame to the DDR2 SDRAM devices.

- 4. For DDR2-667 (PC2-5300), this is measured from the latest DQS input to the AMB to the start of the matching data frame at the northbound FBDIMM outputs.

# 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) IDD Specifications and Conditions

## **IDD Specifications and Conditions**

### **Assumptions for All Parameters**

- primary channel drive strength at 100 percent with de-emphasis at –6.5dB, secondary channel drive strength at 60 percent with de-emphasis at –3dB when enabled.

- Address and data fields are pseudo-random, which provides a 50 percent toggle rate on DDR2 SDRAM data lines and link lanes when data is being transferred.

- Assuming 1 ACTIVATE command and 1 READ/WRITE command per BL = 4 transfer, BL = 4.

- Ten southbound lanes and 14 northbound lanes are enabled and active.

#### SPD-specific assumptions:

- Number of devices on the specific FBDIMM assumed

- Termination of command, address, and control is actual value used on the FBDIMM

- ECC as per the specific FBDIMM

- SPD specifies ΔT

#### AMB power-specification assumptions:

- Specific ECC FBDIMM assumed (72-bit data, 14 lanes northbound with DDR2 SDRAMs as defined in configuration options of this data sheet)

- Modeled with  $27\Omega$  termination for command, address, and clocks, and  $47\Omega$  termination for control

- AMB specification specifies current for each rail

#### Table 9: DDR2 IDD Specifications and Conditions – 4GB

| Parameter/Condition                                                                                                                                                                                                         | Symbol       | -667 | -53E | Units |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|------|-------|

| <b>Idle current, single or last FBDIMM:</b> L0 state, idle (0 BW); primary channel enabled, secondary channel disabled, CKE HIGH; command and address lines stable, DDR2 SDRAM clock active.                                | IDD_IDLE_0   | TBD  | TBD  | mA    |

| <b>Idle current, first FBDIMM:</b> L0 state, idle (0 BW); primary and secondary channels enabled, CKE HIGH; command and address lines stable, DDR2 SDRAM clock active.                                                      | IDD_IDLE_1   | TBD  | TBD  | mA    |

| <b>Idle current, DDR2 SDRAM power-down:</b> L0 state, idle (0 BW); primary and secondary channels enabled, CKE HIGH; command and address lines floated, DDR2 SDRAM clock active; ODT and CKE driven LOW.                    | IDD_IDLE_2   | TBD  | TBD  | mA    |

| <b>Active Power:</b> L0 state; 50% DDR2 SDRAM BW, 67% READ, 33% WRITE; primary and secondary channels enabled, CKE HIGH; DDR2 SDRAM clock active.                                                                           | IDD_ACTIVE_1 | TBD  | TBD  | mA    |

| <b>Active Power, data pass-through:</b> L0 state; 50% DDR2 SDRAM BW to downstream FBDIMM, 67% READ, 33% WRITE; primary and secondary channels enabled; command and address lines stable, CKE HIGH; DDR2 SDRAM clock active. | IDD_ACTIVE_2 | TBD  | TBD  | mA    |

| <b>Channel standby:</b> Average power over 42 frames where the channel enters and exits L0s; DDR2 SDRAM devices Idle (0 BW); CKE LOW; command and address lines floated; DDR2 SDRAM lock active, ODE and CKE driven LOW.    | IDD_L0s      | TBD  | TBD  | mA    |

| <b>Training:</b> Primary and secondary channels enabled; 100% toggle on all channel lanes; DDR2 SDRAM devices idle (0 BW); CKE HIGH, command and address lines stable; DDR2 SDRAM clock active.                             | IDD_TRAINING | TBD  | TBD  | mA    |

### 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) **IDD Specifications and Conditions**

**Reference Clock Input Specifications** Table 10:

| Parameter                                    | Symbol               | Min              | Max        | Unit    | Notes  |

|----------------------------------------------|----------------------|------------------|------------|---------|--------|

| Reference clock frequency                    | fsck                 | 133.33           | 200        | MHz     | 1, 2   |

| Rise time, fall time                         | TSCK-RISE, TSCK-FALL | 175              | 700        | ps      | 3      |

| Voltage high                                 | Vsck-high            | 660              | 850        | mV      |        |

| Voltage low                                  | Vsck-low             | -150             |            | mV      |        |

| Absolute crossing point                      | Vcross-abs           | 250              | 550        | mV      | 4      |

| Relative crossing point                      | Vcross-rel           | calculated       | calculated | _       | 4, 5   |

| Percent mismatch between rise and fall times | TSCK-RISE-FALL-MATCH | -                | 10         | %       |        |

| Duty cycle of reference clock                | TSCK-DUTYCYCLE       | 40               | 60         | %       |        |

| Clock leakage current                        | II-CK                | -10              | 10         | μΑ      | 6, 7   |

| Clock input capacitance                      | CI-CK                | 0.5              | 2          | pF      | 7      |

| Clock input capacitance delta                | Cı_ck(d)             | -0.25            | 0.25       | pF      | 8      |

| Transport delay                              | T1                   |                  | 5          | ns      | 9, 10  |

| Phase jitter sample size                     | NSAMPLE              | 10 <sup>16</sup> | _          | Periods | 11     |

| Reference clock jitter, filtered             | Tref-jitter          | -                | 40         | ps      | 12, 13 |

| Reference clock deterministic jitter         | Tref-dj              | _                | TBD        | ps      |        |

- Notes: 1. 133 MHz for PC2-4200 and 166 MHz for PC2-5300.

- 2. Measured with SSC disabled.

- 3. Measured differentially through the range of 0.175V to 0.525V.

- 4. The crossing point must meet the absolute and relative crossing point specification simultaneously.

- 5. VCROSS\_REL\_(MIN) and VCROSS\_REL\_(MAX) are derived using the following calculation: MIN =  $0.5 (V_{HAVG} - 0.710) + 0.250$ ; and MAX =  $0.5 (V_{HAVG} - 0.710) + 0.550$ , where  $V_{HAVG}$  is the average of Vsck-HIGHM.

- 6. Measured with a single-ended input voltage of 1V.

- 7. Applies to reference clocks SCK and SCK#.

- 8. Difference between SCK and SCK# input.

- 9. T1 = |Tdatapath Tclockpath| (excluding PLL loop delays). This parameter is not a direct clock output parameter but it indirectly determines the clock output parameter TREF-JITTER.

- 10. The net transport delay is the difference in time of flight between associated data and clock paths. The data path is defined from the reference clock source, through the TX, to data arrival at the data sampling point in the RX. The clock path is defined from the reference clock source to clock arrival at the same sampling point. See Figure 3-3 of the JEDEC specification. The path delays are caused by copper trace routes, on-chip routing, on-chip buffering, etc. They include the time-of-flight of interpolators or other clock adjustment mechanisms. They do not include the phase delays caused by finite PLL loop bandwidth because these delays are modeled by the PLL transfer functions.

- 11. Direct measurement of phase jitter records over 1,016 periods is impractical. It is expected that the jitter will be measured over a smaller, yet statistically significant, sample size and the total jitter at 10<sup>16</sup> samples extrapolated from an estimate of the sigma of the random jitter components.

- 12. Measured with SSC-enabled on reference clock generator.

- 13. As measured after the phase jitter filter. This number is separate from the receiver jitter budget that is defined by the TRXTotal-MIN parameters.

Table 11: **VTT Currents**

| Description                                | Symbol | Тур | Мах | Unit |

|--------------------------------------------|--------|-----|-----|------|

| Idle current, DDR2 SDRAM device power-down | ITT1   | 500 | 700 | mA   |

| Active power, 50% DDR2 SDRAM BW            | ITT2   | 500 | 700 | mA   |

## **Differential Transmitter and Receiver Specifications**

## Table 12: Differential Transmitter Output Specifications

| Parameter                                                              | Symbol                            | Min  | Мах       | Unit | Comments, Notes                                                               |

|------------------------------------------------------------------------|-----------------------------------|------|-----------|------|-------------------------------------------------------------------------------|

| Differential peak-to-peak output voltage for large voltage swing       | $V_{TX\text{-}DIFFp\text{-}p\_L}$ | 900  | 1,300     | mV   | EQ 1, Note 1                                                                  |

| Differential peak-to-peak output voltage for regular voltage swing     | V <sub>TX-DIFFP-p_R</sub>         | 800  | -         | mV   | EQ 1, Note 1                                                                  |

| Differential peak-to-peak output voltage for small voltage swing       | V <sub>TX-DIFF</sub> p-p_S        | 520  | _         | mV   | EQ 1, Note 1                                                                  |

| DC common code output voltage for large voltage swing                  | $V_{TX\text{-}CM_{L}}$            | -    | 375       | mV   | EQ 2, Note 1                                                                  |

| DC common code output voltage for small voltage swing                  | $V_{TX\text{-}CM_{S}}$            | 135  | 280       | mV   | EQ 2, Note 1, 2                                                               |

| De-emphasized differential output voltage ratio for –3.5dB de-emphasis | V <sub>TX-DE-3.5-Ratio</sub>      | -3.0 | -4.0      | dB   | Note 1, 3, 4                                                                  |

| De-emphasized differential output voltage ratio for –6.0dB de-emphasis | V <sub>TX-DE-6.0-Ratio</sub>      | -5.0 | -7.0      | dB   | Note 1, 3, 4                                                                  |

| AC peak-to-peak common mode output voltage for large swing             | V <sub>TX-CM-ACp-p-L</sub>        | _    | 90        | mV   | EQ 7, Note 1, 5                                                               |

| AC peak-to-peak common mode output voltage for regular swing           | V <sub>TX-CM-ACp-p-R</sub>        | _    | 80        | mV   | EQ 7, Note 1, 5                                                               |

| AC peak-to-peak common mode output voltage for small swing             | V <sub>TX-CM-ACp-p-S</sub>        | _    | 70        | mV   | EQ 7, Note 1, 5                                                               |

| MAX single-ended voltage in EI condition DC + AC                       | $V_{TX-IDLE-SE}$                  | _    | 50        | mV   | Note 6                                                                        |

| MAX single-ended voltage in EI condition DC + AC                       | $V_{TX-IDLE-SE-DC}$               | _    | 20        | mV   | Note 6                                                                        |

| MAX peak-to-peak differential voltage in El condition                  | V <sub>TX-IDLE-DIFFP-p</sub>      | _    | 40        | mV   |                                                                               |

| Single-ended voltage (referenced to Vss) on D+/D-                      | V <sub>TX-SE</sub>                | -75  | 750       | mV   | Note 1, 7                                                                     |

| MIN TX eye width, 3.2 and 4.0 Gb/s                                     | T <sub>TX-Eye-MIN</sub>           | 0.7  | -         | UI   | Note 1, 8                                                                     |

| MIN TX eye width 4.8 Gb/s                                              | T <sub>TX-EYE-MIN4.8</sub>        | TBD  | _         | J    | Note 1, 8                                                                     |

| MAX TX deterministic jitter, 3.2 and 4.8 Gb/s                          | T <sub>TX-DJ-DD</sub>             | _    | 0.2       | U    | Note 1, 8, 9                                                                  |

| MAX TX deterministic jitter, 4.8 Gb/s                                  | $T_{TX-DJ-DD-4.8}$                | _    | TBD       | UI   | Note 1, 8, 9                                                                  |

| Instantaneous pulse width                                              | T <sub>TX -PULSE</sub>            | 0.85 |           | UI   | Note 10                                                                       |

| Differential TX output rise/fall time                                  | $T_{TX-RISE}T_{TX-FALL}$          | 30   | 90        | ps   | 20–80% voltage, Note 1                                                        |

| Mismatch between rise and fall times                                   | T <sub>TX-RF-MISMATCH</sub>       | _    | 20        | ps   |                                                                               |

| Differential return loss                                               | $RL_TX\text{-DIFF}$               | 8    | -         | dB   | Meas. 0.1–2.4 GHz, Note 11                                                    |

| Common mode return loss                                                | $RL_{TX-CM}$                      | 6    | _         | dB   | Meas. 0.1–2.4 GHz, Note 11                                                    |

| Transmitter termination impender                                       | $R_{TX}$                          | 41   | 55        | Ω    | 12                                                                            |

| D+/D- TX Impedance difference                                          | R <sub>TX-MATCH-DC</sub>          | _    | 4         | %    | EQ 4; Boundaries are applied separately to high and low output voltage states |

| Lane-to-lane skew at TX                                                | L <sub>TX-SKEW 1</sub>            | _    | 100 + 3UI | ps   | Note 13, 15                                                                   |

| Lane-to-lane skew at TX                                                | L <sub>TX-SKEW 2</sub>            | -    | 100 = 2UI | ps   | Note 14, 15                                                                   |

# 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Differential Transmitter and Receiver Specifications

**Table 12: Differential Transmitter Output Specifications (Continued)**

| Parameter                         | Symbol                         | Min               | Мах | Unit | Comments, Notes |

|-----------------------------------|--------------------------------|-------------------|-----|------|-----------------|

| MAX TX drift (resync mode)        | T <sub>TX-DRIFT-RESYNC</sub>   | -                 | 240 | ps   | Note 16         |

| MAX TX drift (resample mode only) | T <sub>TX-DRIFT-RESAMPLE</sub> | -                 | 120 | ps   | Note 16         |

| Bit error ratio                   | BER                            | 10 <sup>-12</sup> | _   | _    | Note 17         |

Notes:

- 1. Specified at the package pins into a timing and voltage compliance test load as shown in Figure 4-2 and in steps outlined in 4.1.2.1 of the JEDEC specification. Common-mode measurements to be performed using a 101010 pattern.

- 2. The transmitter designer should not artificially elevate the common mode in order to meet this specification.

- 3. This is the ratio of the VTX-DIFFp-p of the second and following bits after a transition divided by the VTX-DIFFp-p of the first bit after a transition.

- 4. De-emphasis shall be disabled in the calibration state.

- 5. Includes all sources of AC common mode noise.

- 6. Single-ended voltages below that value that are simultaneously detected on D+ and D- are interpreted as the EI condition.

- 7. The maximum value is specified to be at least (VTX-DIFFp-pL/4) + VTX-CML + (VTX-CM-ACp-p/2).

- 8. This number does not include the effects of SSC or reference clock jitter.

- 9. Defined as the expected maximum jitter for the given probability as measured in the system (TJ), less the unbounded jitter.

- 10. Pulse width measure at 0V differential.

- 11. One of the components that contribute to the deterioration of the return loss is the ESD structure which must be carefully designed.

- 12. The termination small signal resistance; tolerance across voltages from 100mV to 400mV shall not exceed ±5W with regard to the average of the values measured at 100mV and 400mV for that pin.

- 13. Lane-to-lane skew at the transmitter pins for an end component.

- 14. Lane-to-lane skew at the transmitter pins for an intermediate component (assuming zero Lane-to-lane skew at the receiver pins of the incoming port).

- 15. This is a static skew. An FBDIMM component is not allowed to change its lane-to-lane phase relationship after initialization.

- 16. Measured from the reference clock edge to the center of the output eye. This specification must be met across specified voltage and temperature ranges for a single component. Drift rate change is significantly below the tracking capability of the receiver.

- 17. BER per differential lane.

$$V_{\text{TX-DIFF}p-p} = 2 \times |V_{\text{TX-D+}} - V_{\text{TX-D-}}|$$

(EQ 1)

$$V_{TX-CM} = DC_{(AVG)} \text{ of } (|V_{TX-D+} + V_{TX-D-}|/2)$$

(EQ 2)

$$V_{\text{TX-CM-AC}} = ((\text{Max} | V_{\text{TX-D+}} + V_{\text{TX-D-}} |)/2) - ((\text{Min} | V_{\text{TX-D+}} + V_{\text{TX-D-}} |)/2)$$

(EQ 3)

$$R_{\text{TX-MATCH-DC}} = 2 \text{ x } ((|R_{\text{TX-D+}} - R_{\text{TX-D-}}|) / (R_{\text{TX-D+}} + R_{\text{TX-D-}}|))$$

(EQ 4)

# 240-Pin 4GB DDR2 SDRAM FBDIMM (DR, FB, x72) Differential Transmitter and Receiver Specifications

**Table 13: Differential Receiver Input Specifications**

| Parameter                                                       | Symbol                                    | Min  | Max               | Unit | Comments, Notes                                                   |

|-----------------------------------------------------------------|-------------------------------------------|------|-------------------|------|-------------------------------------------------------------------|

| Differential peak-to-peak input voltage for large voltage swing | V <sub>RX-DIFF</sub> p-p                  | 170  | TBD               | mV   | EQ 5, Note 1                                                      |

| MAX single-ended voltage in El condition                        | $V_{RX\text{-IDLE-SE}}$                   | -    | 75                | mV   | Note 2, 3                                                         |