#### **General Description**

The MAX3507 is a variable-gain power amplifier for use in CATV upstream transmitters. The variable-gain feature has 55dB of dynamic range and is controlled by a 3-wire SPI™ bus. The device is capable of generating +64dBmV output (16QAM/QPSK) when driven with a +34dBmV nominal input signal. The on-chip anti-alias lowpass filter with 75MHz cutoff frequency saves system design cost and space. The optional positive slope generator provides system design flexibility.

The device operates from a single +5V supply and draws 220mA nominal during transmit at max gain (100% duty cycle). For burst-type transmissions, the device is shut off between bursts to minimize noise and save power while still maintaining a match at the output. The device is optimized for high linearity with harmonic levels below -55dBc.

The MAX3507 is available in a 28-pin QFN package and operates over the extended industrial temperature range (-40°C to +85°C).

## **Applications**

Cable Modem Upstream Transmitter Set-Top Box Upstream Transmitter Telephony Over Cable

#### **Features**

- ♦ Built-In 5th-Order Elliptic Anti-Aliasing Filter

- ♦ 5MHz to 65MHz Operation

- ♦ 55dB Gain Control Range

- **♦ Optional Positive Slope Generator**

- ♦ 55dB Spurious-Free Dynamic Range Over **Transmit Band**

## **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX3507EGI | -40°C to +85°C | 28 QFN      |

Pin Configuration appears at end of data sheet.

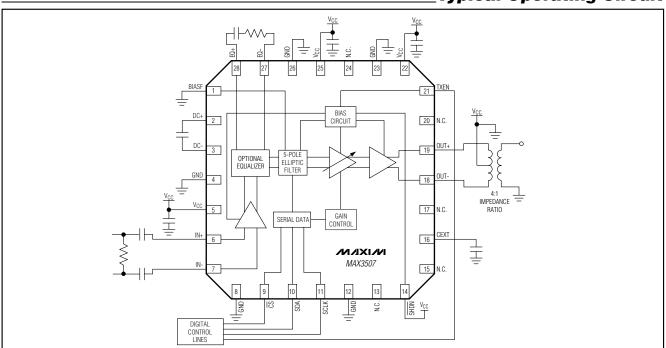

## **Typical Operating Circuit**

SPI is a trademark of Motorola, Inc.

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> , OUT+, OUT- to GND        | 0.5V to +8.0V |

|--------------------------------------------|---------------|

| Input Voltage Levels (all inputs),         |               |

| C <sub>EXT</sub> to GND                    |               |

| Continuous Input Voltage (IN+, IN-)        | 2Vp-p         |

| Continuous Current (OUT+, OUT-)            |               |

| Continuous Power Dissipation ( $T_A = +70$ | °C)           |

| 28-Pin QFN (derate 20.8mW/°C above         | +70°C)1.67W   |

| Operating Temperature Range | 40°C to +85°C  |

|-----------------------------|----------------|

| Junction Temperature        | +150°C         |

| Storage Temperature Range   | 65°C to +125°C |

| Bump Reflow Temperature     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

(MAX3507 EV Kit,  $V_{CC}$  = +4.75V to +5.25V,  $V_{GND}$  = 0,  $V_{TXEN}$  =  $V_{\overline{SHDN}}$  =  $V_{CC}$ , D7 = 1,  $T_A$  = -40°C to +85°C, unless otherwise specified. No input signal applied. A 4:1 (300 $\Omega$  to 75 $\Omega$ ) impedance ratio balun is connected to differential output ports and balun output is terminated into a 75 $\Omega$  load. Typical parameters are at  $V_{CC}$  = +5.0V,  $T_A$  = +25°C.) (Note 1)

| PARAMETER                            | CONDITIONS                                                                | MIN  | TYP | MAX  | UNITS |

|--------------------------------------|---------------------------------------------------------------------------|------|-----|------|-------|

| Supply Voltage                       |                                                                           | 4.75 |     | 5.25 | V     |

|                                      | D7 = 1, gain code = 127 (max gain)                                        |      | 218 | 280  |       |

| Curanhi Currant Transport Mada       | D7 = 1, gain code = 119 (gain of 28dB)                                    |      | 164 |      | A     |

| Supply Current Transmit Mode         | D7 = 1, gain code = 64 (gain of 0dB)                                      |      | 82  |      | mA    |

|                                      | D7 = 0, gain code = 94 (gain of 0dB)                                      |      | 74  |      |       |

| Supply Current Transmit Disable Mode | V <sub>TXEN</sub> = V <sub>EE</sub> , V <sub>SHDN</sub> = V <sub>CC</sub> |      | 45  | 59   | mA    |

| Shutdown Supply Current              | V <sub>TXEN</sub> = X, V <del>SHDN</del> = V <sub>EE</sub>                |      | 1   |      | μΑ    |

| LOGIC INPUTS                         |                                                                           | ·    |     |      |       |

| Input HIGH Voltage Threshold         |                                                                           | 2.0  |     |      | V     |

| Input LOW Voltage Threshold          |                                                                           |      |     | 0.8  | V     |

| Input HIGH Current                   |                                                                           |      |     | 100  | μΑ    |

| Input LOW Current                    |                                                                           | -100 |     |      | μΑ    |

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX3507 EV Kit,  $V_{CC}$  = +4.75V to +5.25V,  $V_{GND}$  = 0,  $V_{TXEN}$  =  $V_{\overline{SHDN}}$  =  $V_{CC}$ ,  $V_{IN}$  = +34dBmV differential,  $T_A$  = -40°C to +85°C, unless otherwise specified. A 4:1 impedance ratio (300 $\Omega$  to 75 $\Omega$ ) balun is connected to differential output ports and balun output is terminated into a 75 $\Omega$  load. Typical parameters are at  $V_{CC}$  = +5.0V,  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                      | C                                                                       | CONDITIONS                                              | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------|-------|-------|-------|-------|

|                                                |                                                                         | D7 = 1, gain code = 125                                 | 29.6  | 31.1  | 32.6  |       |

|                                                |                                                                         | D7 = 1, gain code = 119                                 | 26.8  | 28.3  | 29.8  |       |

|                                                |                                                                         | D7 = 1, gain code = 104                                 | 19.5  | 20.9  | 22.3  |       |

|                                                | $f_{IN} = 5MHz$ ,                                                       | D7 = 1, gain code = 84                                  | 9.7   | 10.9  | 12.1  |       |

|                                                | $T_A = 0$ °C to +85°C (Note 2)                                          | D7 = 1, gain code = 64                                  | -0.7  | 0.5   | 1.7   |       |

| Voltage Gain (A <sub>V</sub> )                 | (14010 2)                                                               | D7 = 0, gain code = 74                                  | -10.5 | -9.3  | -8.1  | dB    |

|                                                |                                                                         | D7 = 0, gain code = 54                                  | -20.4 | -19.1 | -17.8 |       |

|                                                |                                                                         | D7 = 0, gain code = 42                                  | -27.2 | -25.7 | -24.2 | Ī     |

|                                                | $f_{IN} = 65MHz$ ,<br>$T_A = 0^{\circ}C$ to $+85^{\circ}C$<br>(Note 3)  | D7 = 1, gain code = 127                                 | 29.0  |       |       |       |

| Onio Flatono                                   | $V_{OUT} = 61dBmV, f_{IN} = 4$                                          | 2MHz, equalizer disabled (Note 3)                       | -1.1  | -0.5  | +0.2  | -ID   |

| Gain Flatness                                  | $V_{OUT} = 61dBmV, f_{IN} = 6$                                          | 5MHz, equalizer disabled (Note 3)                       | -2.1  | -0.7  | +0.3  | dB    |

|                                                | $f_{IN} = 5MHz$ to $65MHz$ , $\rho$                                     | $A_V = -26$ dB to $+30$ dB                              |       | 0.5   |       |       |

| Gain Step Size                                 | f <sub>IN</sub> = 5MHz to 65MHz, transition of D0, D1                   | $A_V = -26$ dB to $+30$ dB, any 2-bit                   | 0.7   | 1.0   | 1.3   | dB    |

|                                                | $f_{IN} = 5MHz$ to 42MHz, I gain code = 81, $T_A = 0$                   | D7 = 0, gain code = 109; D7 = 1,<br>°C to +85°C         | 0.6   | 1.0   | 1.4   |       |

| Transmit-Disable Mode Noise                    | Any BW = 160kHz from (Note 3)                                           | n 5MHz to 65MHz, TXEN = V <sub>EE</sub>                 |       |       | -64   | dBmV  |

| Isolation in Transmit Disable Mode             | TXEN = V <sub>EE</sub> , f <sub>IN</sub> = 5MH                          | Iz to 65MHz                                             |       | 70    |       | dB    |

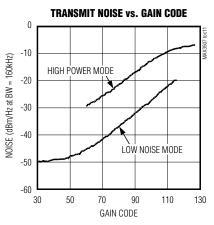

| Transmit Mode Noise                            | Any BW = 160kHz from<br>+30dB (Note 3)                                  | n 5MHz to 65MHz, gain = -26dB to                        |       |       | -54.5 | dBc   |

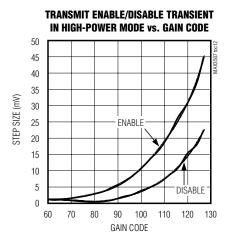

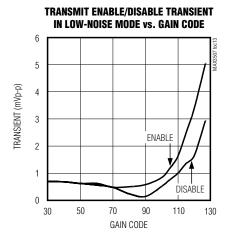

| Transmit Enable Transient Duration             | TXEN input rise/fall time TA = +25°C (Notes 3, 4                        | •                                                       |       |       | 2     | μs    |

| Transmit Disable Transient Duration            | TXEN input rise/fall time TA = +25°C (Notes 3, 4                        | ·                                                       |       |       | 2     | μs    |

| Transmit Disable/Transmit                      | D7 = 1, gain code = 11                                                  | 19 (A <sub>V</sub> = >27dB), $T_A$ = +25°C              |       |       | 100   | .,    |

| Enable Transient Step Size                     | D7 = 0, gain code = 94                                                  | 1 (A <sub>V</sub> = 0), T <sub>A</sub> = +25°C (Note 3) |       | 1.5   | 5.2   | mVp-p |

| Input Impedance                                | $f_{IN} = 5MHz$ to $65MHz$ , s                                          | single ended (Note 3)                                   | 0.8   |       |       | kΩ    |

| Output Return Loss                             | f <sub>IN</sub> = 5MHz to 42MHz ir<br>gain code = 125 (A <sub>V</sub> = |                                                         |       | 10    |       | dB    |

| Output Return Loss in Transmit<br>Disable Mode | $f_{IN} = 5MHz$ to 42MHz in $\frac{1}{2}$                               | 75Ω system, TXEN = V <sub>EE</sub> (Note 5)             |       | 10    |       | dB    |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX3507 EV Kit,  $V_{CC} = +4.75V$  to +5.25V,  $V_{GND} = 0$ ,  $V_{TXEN} = V_{\overline{SHDN}} = V_{CC}$ ,  $V_{IN} = +34dBmV$  differential,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise specified. A 4:1 impedance ratio (300 $\Omega$  to 75 $\Omega$ ) balun is connected to differential output ports and balun output is terminated into a 75 $\Omega$  load. Typical parameters are at  $V_{CC} = +5.0V$ ,  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                           | CONDITIONS                                                                         | MIN | TYP   | MAX | UNITS   |

|-------------------------------------|------------------------------------------------------------------------------------|-----|-------|-----|---------|

| Two-Tone Third-Order Distortion     | Input tones at 42MHz and 42.2MHz, both at +31dBmV, VOUT = +58dBmV/tone             |     | -55.4 |     | dBc     |

| Two-Tone mird-Order Distortion      | Input tones at 65MHz and 65.2MHz, both at +31dBmV, V <sub>OUT</sub> = +58dBmV/tone |     | -47.6 |     | ивс     |

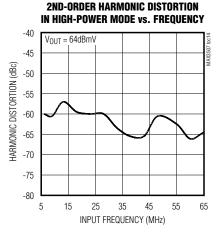

|                                     | $f_{IN} = 33MHz$ , $V_{OUT} = +63dBmV$                                             |     | -58   |     |         |

| 2 <sup>ND</sup> Harmonic Distortion | $f_{IN} = 33MHz$ , $V_{OUT} = +60dBmV$ , $T_A = 0$ °C to $+85$ °C                  |     | -56   | -50 | dBc     |

|                                     | $f_{IN} = 65MHz$ , $V_{OUT} = +60dBmV$                                             |     | -61   |     |         |

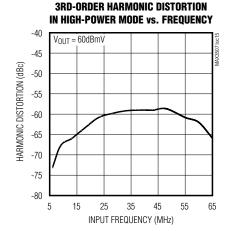

|                                     | $f_{IN} = 22MHz$ , $V_{OUT} = +63dBmV$                                             |     | -53   |     |         |

| 3 <sup>RD</sup> Harmonic Distortion | $f_{IN} = 22MHz$ , $V_{OUT} = +60dBmV$                                             |     | -58   | -51 | dBc     |

|                                     | $f_{IN} = 65MHz$ , $V_{OUT} = +60dBmV$                                             |     | -57   |     |         |

| 1dB Compression Point               | Gain = 26dB, f <sub>IN</sub> = 65MHz                                               |     | 22    |     | dBm     |

| AM to AM                            | Gain = 28dB, $V_{IN}$ = +34dBmV to +38dBmV, $f_{IN}$ = 65MHz                       |     | -0.1  |     | dB      |

| AM to PM                            | Gain = 28dB, $V_{IN}$ = +34dBmV to +38dBmV, $f_{IN}$ = 65MHz                       |     | -1.3  |     | degrees |

| Rejection at 135MHz                 | Referenced to 65MHz                                                                | 36  | 47    |     | dBc     |

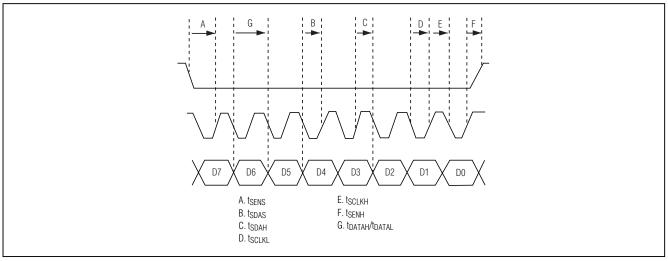

#### **TIMING CHARACTERISTICS**

(MAX3507 EV Kit, V<sub>CC</sub> = +4.75V to +5.25V, V<sub>GND</sub> = 0, V<sub>TXEN</sub> = V<sub>SHDN</sub> = V<sub>CC</sub>, T<sub>A</sub> = +25°C, unless otherwise specified.) (Note 3)

| PARAMETER                  | SYMBOL | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------------|--------|------------|-----|-----|-----|-------|

| SEN to SCLK Rise Set Time  | tsens  |            | 20  |     |     | ns    |

| SEN to SCLK Rise Hold Time | tsenh  |            | 10  |     |     | ns    |

| SDA to SCLK Setup Time     | tsdas  |            | 10  |     |     | ns    |

| SDA to SCLK Hold Time      | tsdah  |            | 20  |     |     | ns    |

| SDA Pulse-Width High       | tdatah |            | 50  |     |     | ns    |

| SDA Pulse-Width Low        | tdatal |            | 50  |     |     | ns    |

| SCLK Pulse-Width High      | tsclkh |            | 50  |     |     | ns    |

| SCLK Pulse-Width Low       | tsclkl |            | 50  |     |     | ns    |

- Note 1: Guaranteed by design and characterization to ±3 sigma for TA < +25°C, unless otherwise specified.

- Note 2: AC gain correlated to DC gain measurements to ±3 sigma.

- Note 3: Guaranteed by design and characterization to ±6 sigma.

- **Note 4:** All transients comply with DOCSIS 1.1 limits for transmit power ripple of ±0.1dB.

- Note 5: Does not include output matching; see *Output Match* in the *Applications* section.

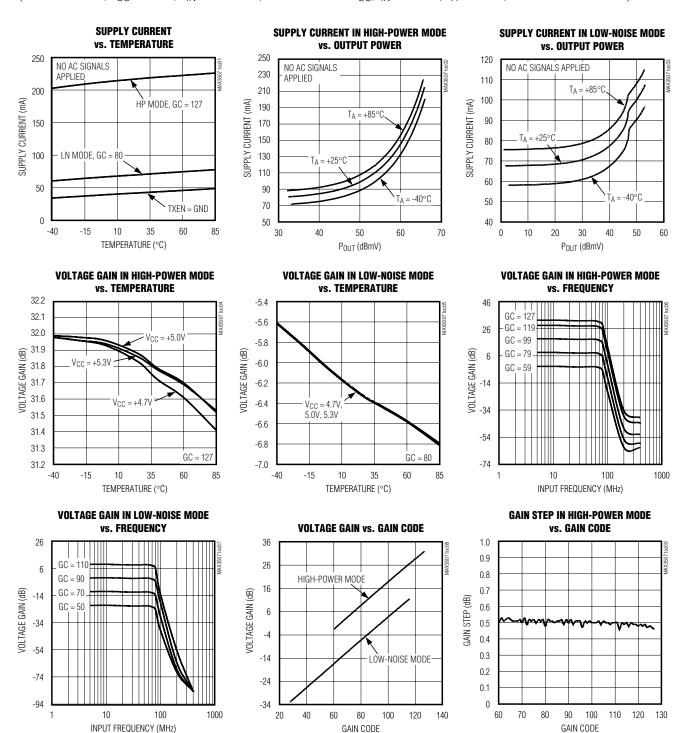

## **Typical Operating Characteristics**

(MAX3507 EV Kit, V<sub>CC</sub> = +5.0V, V<sub>IN</sub> = +34dBmV, TXEN = SHDN = V<sub>CC</sub>, f<sub>IN</sub> = 20MHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

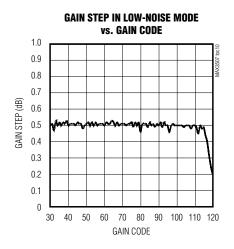

## **Typical Operating Characteristics (continued)**

(MAX3507 EV Kit,  $V_{CC} = +5.0V$ ,  $V_{IN} = +34dBmV$ , TXEN =  $\overline{SHDN} = V_{CC}$ ,  $f_{IN} = 20MHz$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

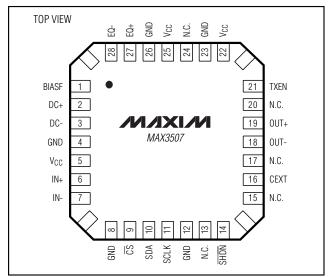

## **Pin Description**

| PIN                | NAME  | DESCRIPTION                                                                                                                                                          |

|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | BIASF | Filter Bias. Connect to GND.                                                                                                                                         |

| 2                  | DC+   | Filter Offset Correction. Connect 0.1µF capacitor between this pin and DC                                                                                            |

| 3                  | DC-   | Filter Offset Correction. Connect 0.1µF capacitor between this pin and DC+.                                                                                          |

| 4, 8, 12, 23, 26   | GND   | Ground                                                                                                                                                               |

| 5, 22, 25          | Vcc   | +5V Supply. Bypass this pin to GND with a 0.1µF capacitor as close to the part as possible.                                                                          |

| 6                  | IN+   | Positive Input. Along with IN-, this port forms a high-impedance differential input to the filter.                                                                   |

| 7                  | IN-   | Negative Input. When not used, this port must be AC-coupled to ground. See IN+.                                                                                      |

| 9                  | CS    | Serial Interface Enable (Chip Select). TTL-compatible input. See Serial Interface section.                                                                           |

| 10                 | SDA   | Serial Interface Data (Serial Data). TTL-compatible input. See Serial Interface section.                                                                             |

| 11                 | SCLK  | Serial Interface Clock (Serial Clock). TTL-compatible input. See Serial Interface section.                                                                           |

| 13, 15, 17, 20, 24 | N.C.  | No Connection. Not internally connected.                                                                                                                             |

| 14                 | SHDN  | Shutdown. When SHDN is set low, all functions (including the serial interface) are disabled.                                                                         |

| 16                 | CEXT  | RF Output Bypass. Bypass to ground with a 0.1µF capacitor.                                                                                                           |

| 18                 | OUT-  | Negative Output. Along with OUT+, this port forms a $300\Omega$ impedance output. This port is matched to a $75\Omega$ load using a 2:1 (voltage ratio) transformer. |

| 19                 | OUT+  | Positive Output. See OUT                                                                                                                                             |

| 21                 | TXEN  | Signal Path Enable. Setting this pin low turns off the PGA and power amplifier, leaving the filter and serial interface enabled to save the last gain setting.       |

| 27                 | EQ+   | Positive Equalizer. Connect an RC network if equalization of the filter passband is desired; leave open otherwise. See <i>Typical Operating Characteristics</i> .    |

| 28                 | EQ-   | Negative Equalizer. Connect an RC network if equalization of the filter passband is desired; leave open otherwise. See <i>Typical Operating Characteristics</i> .    |

## **Detailed Description**

#### **Internal Filter**

The internal filter consists of an input transconductance amplifier, a balanced fifth-order elliptic active lowpass filter, and an offset-correction feedback network. The signal at the output of the filter is level-shifted into the programmable-gain amplifier.

The transconductance amplifier provides a high input impedance to the user, and current drives the filter to minimize insertion loss. The filter is a Gm-C topology to provide sufficient bandwidth and linearity. The cutoff frequency of the filter is fixed at 75MHz, while the specified stopband attenuation is met at 120MHz.

The internal offset-correction feedback network removes any DC offset at the output of the filter. An offset voltage at this node would generate a transient during a TX-enable or -disable transition, which would not be acceptable. The offset-correction loop effectively AC-couples the filter output to the programmable-gain

amplifier input. The network generates a highpass corner frequency at:

$$f_{-3dB}(kHz) = 12.5/C(\mu F)$$

Specified performance is achieved when the input is driven differentially. The MAX3507 may be driven single-ended. To drive the device in this manner, one of the input pins must be capacitively coupled to ground. Use a capacitor whose value is large enough to allow for a low-impedance path to ground at the lowest frequency of operation. For operation down to 5MHz, a 0.001µF capacitor is suggested.

#### Programmable-Gain Amplifier

The programmable-gain amplifier (PGA) consists of the variable-gain amplifier (VGA) and the digital-to-analog converter (DAC), which provide better than 55dB of output-level control in 0.5dB steps. The PGA is implemented as a programmable Gilbert-cell attenuator. It uses a differential architecture to achieve maximum linearity. The gain of the PGA is determined by a 7-bit

word (D6–D0) programmed through the serial data interface (Tables 1 and 2).

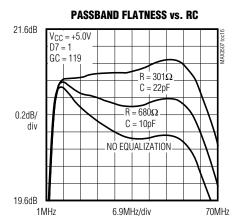

#### **Equalizer Function**

It is possible to add passband amplitude equalization to the MAX3507. This is accomplished by adding polezero peaking to the Gm stage of the PGA. Placing a series RC network between pins EQ+ and EQ- realizes the peaking function. Refer to *Typical Operating Characteristics* for typical values and the associated degree of equalization.

#### **Power Amplifier**

The power amplifier is a Class A differential amplifier capable of driving +64dBmV (QPSK) differentially. This architecture provides superior even-order distortion performance but requires that a transformer be used to convert to a single-ended output. In transmit-disable mode, the output amplifier is shut off. Disabling the output devices also allows the lowest standby noise.

To achieve the proper load line, the output impedance of the power amplifier is  $300\Omega$  differential. To match the output impedance to a  $75\Omega$  load, the transformer must have a turns ratio (voltage ratio) of 2:1 (4:1 impedance ratio). The differential amplifier is biased directly from the +5V supply using the center tap of the output transformer. This provides a significant benefit when switching between transmit mode and transmit disable mode. Stored energy due to bias currents will cancel within the transformer and prevent switching transients from reaching the load.

#### Serial Interface

The serial interface has an active-low enable  $(\overline{CS})$  to bracket the data, with data clocked in MSB first on the rising edge of SCLK. Data is stored in the storage latch on the rising edge of  $\overline{CS}$ . The serial interface controls the gain state of the PGA and the output amplifier. Tables 1 and 2 show the register format. Serial interface timing is shown in Figure 1.

## \_Applications Information

#### **Transmit High-Power and Low-Noise Modes**

The MAX3507 has two transmit modes, high-power (HP) mode and low-noise (LN) mode. Each of these modes is controlled by D7 (MSB) of the 8-bit programming word. When D7 is a logical 1, HP mode is enabled. When D7 is a logical 0, LN mode is enabled.

Each of these modes is characterized by the activation of a distinct output stage. In HP mode, the output stage exhibits a gain that is 15dB higher than gain in LN mode. In LN mode, the lower gain output stage allows

**Table 1. Serial-Interface Control Word**

| BIT     | MNEMONIC | DESCRIPTION                         |  |  |  |  |  |

|---------|----------|-------------------------------------|--|--|--|--|--|

| 7 (MSB) | D7       | High-Power/Low-Noise Mode<br>Select |  |  |  |  |  |

| 6       | D6       | Gain Code, Bit 6                    |  |  |  |  |  |

| 5       | D5       | Gain Code, Bit 5                    |  |  |  |  |  |

| 4       | D4       | Gain Code, Bit 4                    |  |  |  |  |  |

| 3       | D3       | Gain Code, Bit 3                    |  |  |  |  |  |

| 2       | D2       | Gain Code, Bit 2                    |  |  |  |  |  |

| 1       | D1       | Gain Code, Bit 1                    |  |  |  |  |  |

| 0 (LSB) | D0       | Gain Code, Bit 0                    |  |  |  |  |  |

for significantly lower output noise and lower transmit/transmit disable transients.

The full range of gain codes (D6–D0) may be used in either mode. For DOCSIS applications, HP mode is recommended for output levels at or above +42dBmV, and LN mode is recommended for output levels below +42dBmV.

#### **Shutdown Mode**

In normal operation, the shutdown pin  $\overline{(SHDN)}$  is held high. When  $\overline{SHDN}$  is set low, all circuits within the device are disabled. Only leakage currents flow in this state. Data stored within the serial data interface latches will be lost upon entering this mode. Current consumption is reduced to 1µA (typ) in shutdown mode.

#### **Output Match**

The MAX3507 output impedance is internally matched to  $300\Omega$ . This  $300\Omega$  internal resistor is placed across the OUT+ and OUT- terminals. When used in conjunction with a 2:1 (voltage ratio) transformer, the MAX3507 output impedance is matched to  $75\Omega$ .

To improve the output impedance matching for the highend frequency range (65MHz), a reactive match may be employed as part of the ensuing diplex filter. The reactive match normally consists of a series inductor (180nH typ) followed by a shunt capacitor (33pF typ), and is placed directly after the output transformer. This match will also improve the gain flatness substantially.

As mentioned above, the matching components may be incorporated into the diplex filter design. Optimize the input impedance of the diplex filter to be 35 + j35 (typ) at 65MHz when using the specified output transformer.

#### **Transformer**

To match the output of the MAX3507 to a  $75\Omega$  load, a 2:1 (voltage ratio) transformer is required. This trans-

Figure 1. Serial Interface Timing Diagram

**Table 2. Chip-State Control Bits**

| SHDN | TXEN | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | GAIN STATE<br>(DECIMAL) | GAIN<br>(dB) | STATES                              |

|------|------|----|----|----|----|----|----|----|----|-------------------------|--------------|-------------------------------------|

| 0    | Х    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | _                       | _            | Shutdown                            |

| 1    | 0    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |                         | _            | Transmit Disable Mode               |

| 1    | 1    | 1  | Х  | Х  | Х  | Х  | Χ  | Χ  | Χ  | _                       | _            | Transmit Enable Mode,<br>High Power |

| 1    | 1    | 0  | Х  | Х  | Х  | Х  | Χ  | Χ  | Х  | _                       | _            | Transmit Enable Mode,<br>Low Noise  |

| 1    | 1    | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 48                      | -22.6        | _                                   |

| 1    | 1    | 0  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 80                      | -6.29        | _                                   |

| 1    | 1    | 0  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 110                     | 8.68         |                                     |

| 1    | 1    | 1  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 86                      | 11.69        | _                                   |

| 1    | 1    | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0  | 110                     | 23.7         | _                                   |

| 1    | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 125                     | 31.0         | _                                   |

Typical gain at  $T_A = +25^{\circ}C$  and  $V_{CC} = +5V$ .

former must have adequate bandwidth to cover the intended application. Note that most RF transformers specify bandwidth with a  $50\Omega$  source on the primary and a matching resistance on the secondary winding. Operating in a  $75\Omega$  system will tend to shift the low-frequency edge of the transformer bandwidth specification up by a factor of 1.5, due to primary inductance. Keep this in mind when specifying a transformer.

Bias to the output stage is provided through the center tap on the transformer primary. This greatly diminishes the on/off transients present at the output when switching between transmit and transmit disable modes. Commercially available transformers typically have adequate balance between half-windings to achieve substantial transient cancellation.

Finally, keep in mind that transformer core inductance varies proportionally with temperature. If the application requires low temperature extremes (less than 0°C), adequate primary inductance must be present to sustain low-frequency output capability as temperatures

drop. In general, this will not be a problem, as modern RF transformers have adequate bandwidth.

#### **Input Circuit**

To achieve rated performance, the inputs of the MAX3507 must be driven differentially with an appropriate input level. The differential input impedance is approximately  $4k\Omega$ . The MAX3507 has sufficient gain to produce an output level of +64dBmV (QPSK through a 2:1 transformer) when driven with a +34dBmV input signal. Rated performance is achieved with this input level. When a lower input level is present, the maximum output level will be reduced proportionally and output linearity will increase. If an input level greater than +34dBmV is used, the 3rd-order distortion performance will degrade.

If a single-ended source drives the MAX3507, one of the input terminals must be capacitively coupled to ground (IN+ or IN-). The value of this capacitor must be large enough to look like a short circuit at the lowest frequency of interest. For operation at 5MHz with a  $75\Omega$  source impedance, a value of  $0.001\mu F$  will suffice.

#### Layout Issues

A well-designed PC board is an essential part of an RF circuit. For best performance pay attention to power-supply layout issues as well as the output circuit layout.

#### **Power-Supply Layout**

For minimal coupling between different sections of the MAX3507, the ideal power-supply layout is a star configuration. This configuration has a large-value decou-

## Pin Configuration

pling capacitor at the central power-supply node. The power-supply traces branch out from this node, each going to a separate power-supply node in the circuit. At the end of each of these traces is a decoupling capacitor that provides very low impedance at the frequency of interest. This arrangement provides local power-supply decoupling at each power-supply pin. The power-supply traces must be made as thick as practical.

Ground inductance degrades distortion performance. Therefore, ground plane connections to pins 4, 8, 12, 23, and 26 should be made with multiple vias if necessary.

#### **Output Circuit Layout**

The differential implementation of the MAX3507's output has the benefit of significantly reducing even-order distortion, the most significant of which is 2nd-harmonic distortion. The degree of distortion cancellation depends on the amplitude and phase balance of the overall circuit. It is important to keep the trace lengths from the output pins equal.

**Chip Information**

**TRANSISTOR COUNT: 1457**

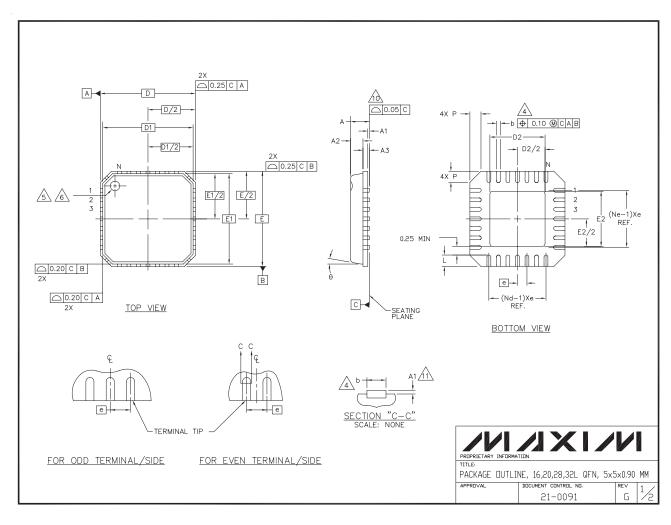

## **Package Information**

## Package Information (continued)

#### NOTES:

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM (.012 INCHES MAXIMUM)

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

3. N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION & Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR INK/ LASER MARKED.

6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS.

- 8. PACKAGE WARPAGE MAX 0.05mm.

APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDED PART OF EXPOSED PAD FROM MEASURING.

- 10, MEETS JEDEC MO220

- 11. THIS PACKAGE OUTLINE APPLIES TO ANVIL SINGULATION (STEPPED SIDES) AND TO SAW SINGULATION (STRAIGHT SIDES) QFN STYLES.

| S         |      | COMMON    |      |                 |  |  |  |  |  |  |  |  |  |  |  |

|-----------|------|-----------|------|-----------------|--|--|--|--|--|--|--|--|--|--|--|

| M         | l DI | MENSION   | 1S   | No <sub>T</sub> |  |  |  |  |  |  |  |  |  |  |  |

| S M B O L | MIN. | NOM.      | MAX. | ŤΕ              |  |  |  |  |  |  |  |  |  |  |  |

| IA I      | 0.80 | 0.90      | 1.00 |                 |  |  |  |  |  |  |  |  |  |  |  |

| A1        | 0.00 | 0.01      | 0.05 |                 |  |  |  |  |  |  |  |  |  |  |  |

| A2        | 0.00 | 0.65      | 1.00 |                 |  |  |  |  |  |  |  |  |  |  |  |

| A3        |      | 0.20 REF. |      |                 |  |  |  |  |  |  |  |  |  |  |  |

| D         |      | 5.00 BSC  |      |                 |  |  |  |  |  |  |  |  |  |  |  |

| D1        |      | 4.75 BSC  |      |                 |  |  |  |  |  |  |  |  |  |  |  |

| E<br>E1   |      | 5.00 BSC  |      |                 |  |  |  |  |  |  |  |  |  |  |  |

| E1        |      | 4.75 BSC  |      |                 |  |  |  |  |  |  |  |  |  |  |  |

| θ         | 0°   | _         | 12°  |                 |  |  |  |  |  |  |  |  |  |  |  |

| Р         | 0    |           | 0.60 |                 |  |  |  |  |  |  |  |  |  |  |  |

| D2        | 1.25 | _         | 3.25 |                 |  |  |  |  |  |  |  |  |  |  |  |

| E2        | 1.25 | _         | 3.25 |                 |  |  |  |  |  |  |  |  |  |  |  |

| S<br>M<br>B |      | VARIAT             |      | N <sub>O</sub> , | S<br>M<br>B | PITCH |                  |      | No <sub>+</sub> | S<br>M<br>B | PITCH |               |      | No, | S<br>M<br>B | PITCH |                  |      | N <sub>O</sub> |

|-------------|------|--------------------|------|------------------|-------------|-------|------------------|------|-----------------|-------------|-------|---------------|------|-----|-------------|-------|------------------|------|----------------|

| ē           | MIN. | NOM.  <br>0.80 BSC | MAX. | 'E               | e           | MIN.  | NOM.<br>0.65 BSC | MAX. | , E             | e           | MIN.  | NOM. 0.50 BSC | MAX. | 'E  | e           | MIN.  | NOM.<br>0.50 BSC | MAX. | - E            |

| N           |      | 16                 |      | 3                | N           |       | 20               |      | 3               | N           |       | 28            |      | 3   | N           |       | 32               |      | 3              |

| Nd          |      | 4                  |      | 3                | Nd          |       | 5                |      | 3               | Nd          |       | 7             |      | 3   | Nd          |       | 8                |      | 3              |

| Ne          |      | 4                  |      | 3                | Ne          |       | 5                |      | 3               | Ne          |       | 7             |      | 3   | Ne          |       | 8                |      | 3              |

| L           | 0.35 | 0.55               | 0.75 |                  | L           | 0.35  | 0.55             | 0.75 |                 | L           | 0.35  | 0.55          | 0.75 |     | L           | 0.30  | 0.40             | 0.50 |                |

| b           | 0.28 | 0.33               | 0.40 | 4                | Ь           | 0.23  | 0.28             | 0.35 | 4               | Ь           | 0.18  | 0.23          | 0.30 | 4   | Ь           | 0.18  | 0.23             | 0.30 | 4              |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.