ISO<sup>2</sup>-CMOS MT8960/61/62/63/64/65/66/67 Integrated PCM Filter Codec

Data Sheet

November 2005

#### **Features**

- ST-BUS<sup>™</sup> compatible

- Transmit/Receive filters & PCM Codec in one I.C

- Meets AT&T D3/D4 and CCITT G711 and G712

- μ-Law: MT8960/62/64/67

- A-Law: MT8961/63/65/67

- Low power consumption:

Op.: 30 mW typ. Stby.: 2.5 mW typ.

- **Digital Coding Options:** ٠ MT8964/65/66/67 CCITT Code MT8960/61/62/63 Alternative Code

- Digitally controlled gain adjust of both filters

- Analog and digital loopback

- Filters and codec independently user accessible for testing

- Powerdown mode available

- 2.048 MHz master clock input

- Up to six uncommitted control outputs

- $\pm 5 \text{ V} \pm 5\%$  power supply

| Order | ring Information                                                                                                                                                                                                                                                                         | 1                                                                                                                       |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

|       | 18 Pin PDIP<br>20 Pin PDIP<br>20 Pin SOIC<br>20 Pin SOIC<br>18 Pin PDIP*<br>20 Pin SOIC*<br>20 Pin SOIC* | Tubes<br>Tubes<br>Tubes<br>Tape & Reel<br>Tubes<br>Tape & Reel<br>Tubes<br>Tubes<br>Tape & Reel<br>Tubes<br>Tape & Reel |

|       |                                                                                                                                                                                                                                                                                          |                                                                                                                         |

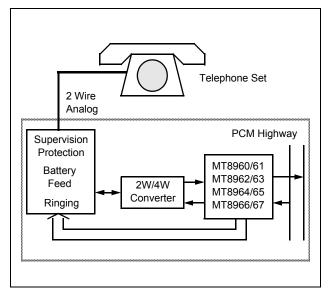

### Description

Manufactured in ISO<sup>2</sup>-CMOS. these integrated filter/codecs are designed to meet the demanding performance needs of the digital telecommunications industry, e.g., PABX, Central Office, Digital telephones.

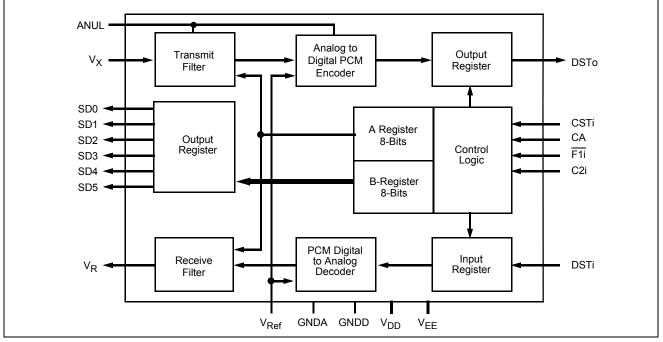

#### Figure 1 - Functional Block Diagram

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2003-2005, Zarlink Semiconductor Inc. All Rights Reserved.

1

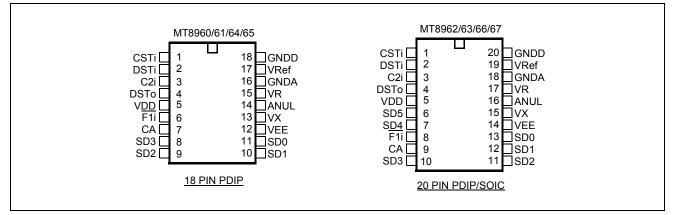

Figure 2 - Pin Connections

#### **Pin Description**

| Pin Name         | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSTi             | <b>Control ST-BUS In</b> is a TTL-compatible digital input used to control the function of the filter/codec.<br>Three modes of operation may be effected by applying to this input a logic high (V <sub>DD</sub> ), logic low (GNDD), or an 8-bit serial word, depending on the logic states of CA and F1i.<br>Functions controlled are: powerdown, filter gain adjust, loopback, chip testing, SD outputs. |

| DSTi             | Data ST-BUS In accepts the incoming 8-bit PCM word. Input is TTL-compatible.                                                                                                                                                                                                                                                                                                                                |

| C2i              | Clock Input is a TTL-compatible 2.048 MHz clock.                                                                                                                                                                                                                                                                                                                                                            |

| DSTo             | <b>Data ST-BUS Out</b> is a three-state digital output driving the PCM bus with the outgoing 8-bit PCM word.                                                                                                                                                                                                                                                                                                |

| $V_{DD}$         | Positive power Supply (+5 V).                                                                                                                                                                                                                                                                                                                                                                               |

| F1i              | <b>Synchronization Input</b> is an active low digital input enabling (in conjunction with CA) the PCM input, PCM output and digital control input. It is internally sampled on every positive edge of the clock, C2i, and provides frame and channel synchronization.                                                                                                                                       |

| CA               | <b>Control Address</b> is a three-level digital input which enables PCM input and output and determines into which control register (A or B) the serial data, presented to CSTi, is stored.                                                                                                                                                                                                                 |

| SD3              | <b>System Drive Output</b> is an open drain output of an N-channel transistor which has its source tied to GNDA. Inactive state is open circuit.                                                                                                                                                                                                                                                            |

| SD4-5            | <b>System Drive Outputs</b> are open drain outputs of N-channel transistors which have their source tied to GNDD. Inactive state is open circuit.                                                                                                                                                                                                                                                           |

| SD0-2            | <b>System Drive Outputs</b> are "Totempole" CMOS outputs switching between GNDD and $V_{DD}$ . Inactive state is logic low.                                                                                                                                                                                                                                                                                 |

| $V_{EE}$         | Negative power supply (-5 V).                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>X</sub>   | Voice Transmit is the analog input to the transmit filter.                                                                                                                                                                                                                                                                                                                                                  |

| ANUL             | Auto Null is used to integrate an internal auto-null signal. A 0.1 $\mu$ F capacitor must be connected between this pin and GNDA.                                                                                                                                                                                                                                                                           |

| V <sub>R</sub>   | Voice Receive is the analog output of the receive filter.                                                                                                                                                                                                                                                                                                                                                   |

| GNDA             | Analog ground (0 V).                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>Ref</sub> | Voltage Reference input to D to A converter.                                                                                                                                                                                                                                                                                                                                                                |

| GNDD             | Digital ground (0 V).                                                                                                                                                                                                                                                                                                                                                                                       |

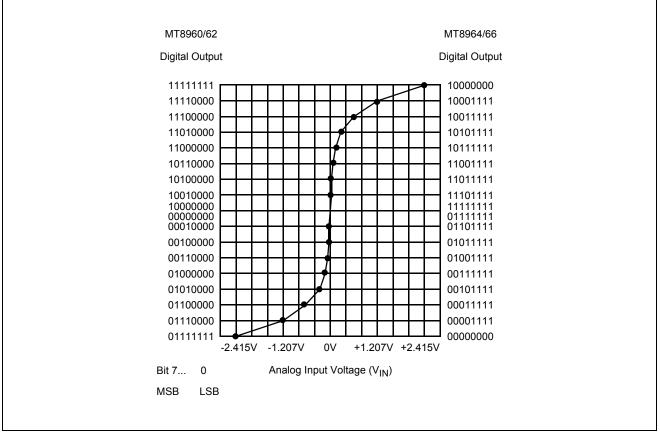

Figure 3 - µ-Law Encoder Transfer Characteristic

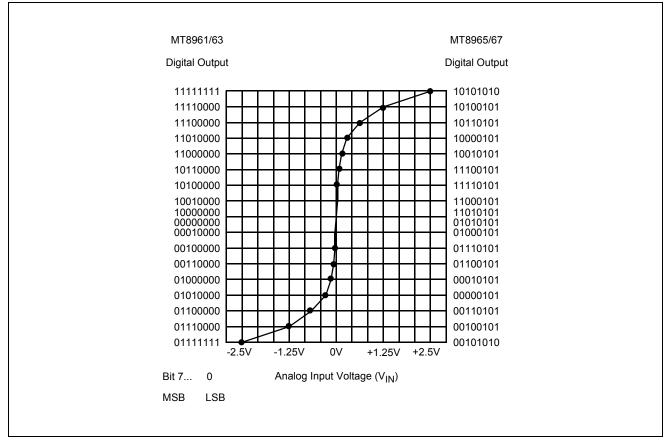

Figure 4 - A-Law Encoder Transfer Characteristic

### **Functional Description**

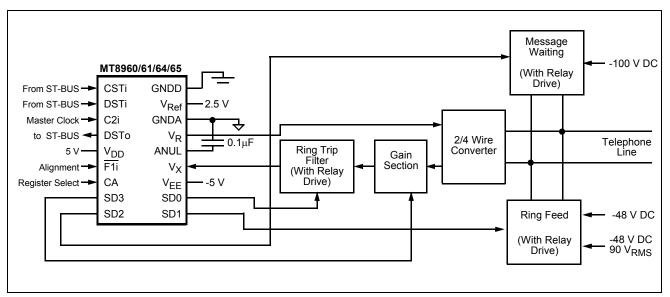

Figure 1 shows the functional block diagram of the MT8960-67. These devices provide the conversion interface between the voiceband analog signals of a telephone subscriber loop and the digital signals required in a digital PCM (pulse code modulation) switching system. Analog (voiceband) signals in the transmit path enter the chip at  $V_X$ , are sampled at 8 kHz, and the samples quantized and assigned 8-bit digital values defined by logarithmic PCM encoding laws. Analog signals in the receive path leave the chip at  $V_R$  after reconstruction from digital 8-bit words.

Separate switched capacitor filter sections are used for bandlimiting prior to digital encoding in the transmit path and after digital decoding in the receive path. All filter clocks are derived from the 2.048 MHz master clock input, C2i. Chip size is minimized by the use of common circuitry performing the A to D and D to A conversion. A successive approximation technique is used with capacitor arrays to define the 16 steps and 8 chords in the signal conversion process. Eight-bit PCM encoded digital data enters and leaves the chip serially on DSTi and DSTo pins, respectively.

### **Transmit Path**

Analog signals at the input (Vx) are firstly bandlimited to 508 kHz by an RC lowpass filter section. This performs the necessary anti-aliasing for the following first-order sampled data lowpass pre-filter which is clocked at 512 kHz. This further bandlimits the signal to 124 kHz before a fifth-order elliptic lowpass filter, clocked at 128 kHz, provides the 3.4 kHz bandwidth required by the encoder section. A 50/60 Hz third-order highpass notch filter clocked at 8 kHz completes the transmit filter path. Accumulated DC offset is cancelled in this last section by a switched-capacitor auto-zero loop which integrates the sign bit of the encoded PCM word, fed back from the codec and

injects this voltage level into the non-inverting input of the comparator. An integrating capacitor (of value between 0.1 and 1  $\mu$ F) must be externally connected from this point (ANUL) to the Analog Ground (GNDA).

The absolute gain of the transmit filter (nominally 0 dB at 1 kHz) can be adjusted from 0 dB to 7 dB in 1 dB steps by means of three binary controlled gain pads.

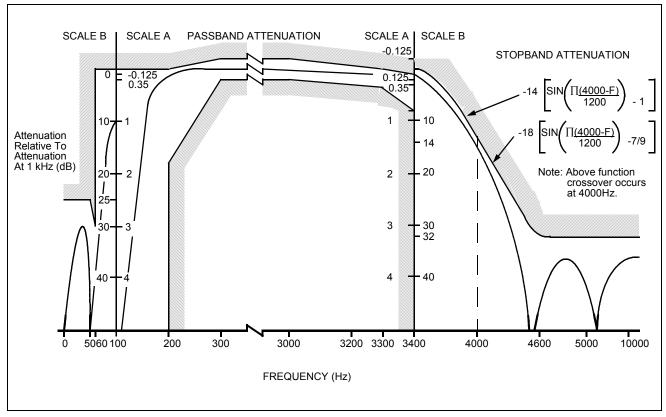

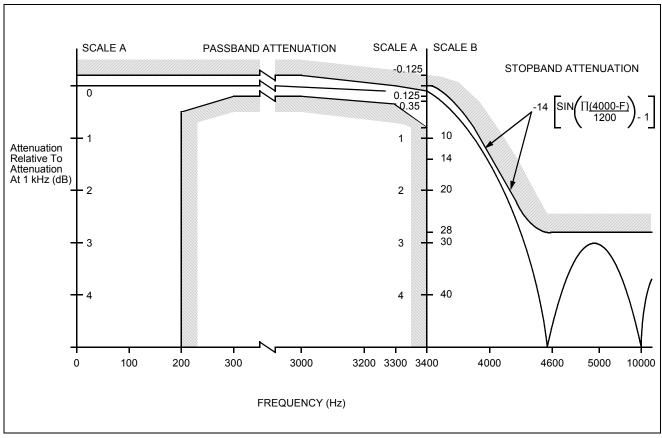

The resulting bandpass characteristics with the limits shown in Figure 10 meet the CCITT and AT&T recommended specifications. Typical attenuations are 30 dB for 0-60 Hz and 35 dB for 4.6 kHz and above.

The filter output signal is an 8 kHz staircase waveform which is fed into the codec capacitor array, or alternatively, into an external capacitive load of 250 pF when the chip is in the test mode. The digital encoder generates an eightbit digital word representation of the 8 kHz sampled analog signal. The first bit of serial data stream is bit 7 (MSB) and represents the sign of the analog signal. Bits 4-6 represent the chord which contains the analog sample value. Bits 0-3 represent the step value of the analog sample within the selected chord. The MT8960-63 provide a sign plus magnitude PCM output code format. The MT8964/66 PCM output code conforms to the AT &T D3 specification, i.e., true sign bit and inverted magnitude bits. The MT8965/67 PCM output code conforms to the CCITT specifications with alternate digit inversion (even bits inverted). See Figs. 3 and 4 for the digital output code corresponding to the analog voltage,  $V_{IN}$ , at  $V_X$  input.

The eight-bit digital word is output at DSTo at a nominal rate of 2.048 MHz, via the output buffer as the first 8-bits of the 125  $\mu$ s sampling frame.

#### **Receive Path**

An eight-bit PCM encoded digital word is received on DSTi input once during the 125  $\mu$ s period and is loaded into the input register. A charge proportional to the received PCM word appears on the capacitor array and an 8 kHz sample and hold circuit integrates this charge and holds it for the rest of the sampling period.

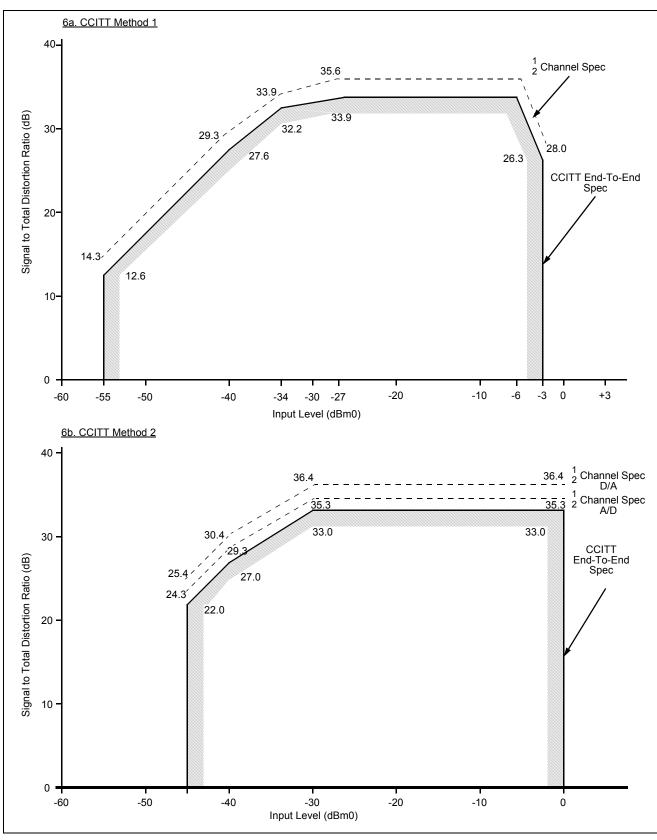

The receive (D/A) filter provides interpolation filtering on the 8 kHz sample and hold signal from the codec. The filter consists of a 3.4 kHz lowpass fifth-order elliptic section clocked at 128 kHz and performs bandlimiting and smoothing of the 8 kHz "staircase" waveform. In addition, sinx/x gain correction is applied to the signal to compensate for the attenuation of higher frequencies caused by the capacitive sample and hold circuit. The absolute gain of the receive filter can be adjusted from 0 dB to -7 dB in 1 dB steps by means of three binary controlled gain pads. The resulting lowpass characteristics, with the limits shown in Figure 11, meet the CCITT and AT & T recommended specifications.

Typical attenuation at 4.6 kHz and above is 30 dB. The filter is followed by a buffer amplifier which will drive 5V peak/peak into a 10k ohm load, suitable for driving electronic 2-4 wire circuits.

## V<sub>Ref</sub>

An external voltage must be supplied to the V<sub>Ref</sub> pin which provides the reference voltage for the digital encoding and decoding of the analog signal. For V<sub>Ref</sub> = 2.5 V, the digital encode decision value for overload (maximum analog signal detect level) is equal to an analog input V<sub>IN</sub> = 2.415 V ( $\mu$ -Law version) or 2.5 V (A-Law version) and is equivalent to a signal level of 3.17 dBm0 or 3.14 dBm0 respectively, at the codec.

The analog output voltage from the decoder at V<sub>R</sub> is defined as:

μ-Law:

$$V_{\text{Ref}} X \quad \left[ \left( \frac{-0.5}{128} \right) + \left( \frac{2^{\text{C}}}{128} \right) \left( \frac{16.5 + S}{33} \right) \right] \pm V_{\text{OFFSET}}$$

A-Law:

$$V_{\text{Ref}} X \quad \left[ \left( \frac{2^{C+1}}{128} \right) \left( \frac{0.5 + S}{32} \right) \right] \pm V_{\text{OFFSET}} C = 0$$

$$V_{Ref} X \quad \left[ \left( \frac{2^{C}}{128} \right) \left( \frac{16.5 + S}{32} \right) \right] \pm V_{OFFSET} C \neq 0$$

where C =chord number (0-7)

S = step number (0-15)

$V_{\text{Ref}}$  is a high impedance input with a varying capacitive load of up to 40 pF.

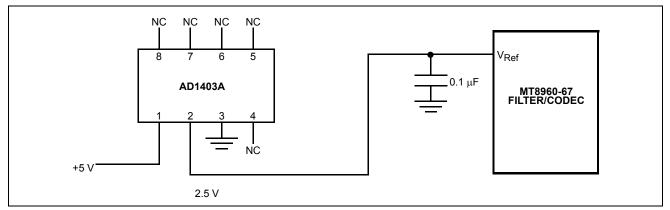

The recommended reference voltage for the MT8960 series of codecs is 2.5 V ±0.5%. The output voltage from the reference source should have a maximum temperature coefficient of 100 ppm/C°. This voltage should have a total regulation tolerance of ±0.5% both for changes in the input voltage and output loading of the voltage reference source. A voltage reference circuit capable of meeting these specifications is shown in Figure 5. Analog Devices'AD1403A voltage reference circuit is capable of driving a large number of codecs due to the high input impedance of the  $V_{Ref}$  input. Normal precautions should be taken in PCB layout design to minimize noise coupling to this pin. A 0.1  $\mu$ F capacitor connected from  $V_{Ref}$  to ground and located as close as possible to the codec is recommended to minimize noise entering through  $V_{Ref}$ . This capacitor should have good high frequency characteristics.

Figure 5 - Typical Voltage Reference Circuit

## Timing

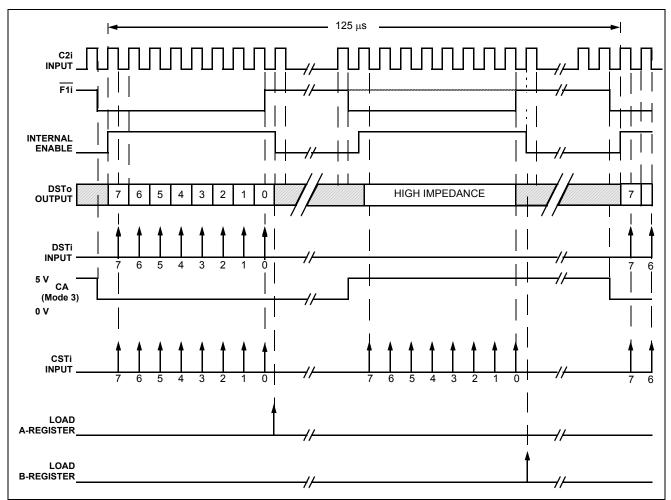

The codec operates in a synchronous manner (see Figure 9a). The codec is activated on the first positive edge of C2i after F1i has gone low. The digital output at DSTo (which is a three-state output driver) will then change from a high impedance state to the sign bit of the encoded PCM word to be output. This will remain valid until the next positive edge, when the next most significant bit will be output.

On the first negative clock edge (after  $\overline{F1i}$  signal has been internally synchronized and CA is at GNDD or V<sub>EE</sub>) the logic signal present at DSTi will be clocked into the input shift register as the sign bit of the incoming PCM word.

The eight-bit word is thus input at DSTi on negative edges of C2i and output at DSTo on positive edges of C2i.

$\overline{F1i}$  must return to a high level after the eighth clock pulse causing DSTo to enter high impedance and preventing further input data to DSTi.  $\overline{F1i}$  will continue to be sampled on every positive edge of C2i. (Note:  $\overline{F1i}$  may subsequently be taken low during the same sampling frame to enable entry of serial data into CSTi. This occurs usually mid-frame, in conjunction with CA=V<sub>DD</sub>, in order to enter an 8-bit control word into Register B. In this case, PCM input and output are inhibited by CA at V<sub>DD</sub>.)

Internally the codec will then perform a decode cycle on the newly input PCM word. The sampled and held analog signal thus decoded will be updated 25  $\mu$ s from the start of the cycle. After this the analog input from the filter is sampled for 18  $\mu$ s, after which digital conversion takes place during the remaining 82  $\mu$ s of the sampling cycle.

Since a single clock frequency of 2.048 MHz is required, all digital data is input and output at this rate. DSTo, therefore, assumes a high impedance state for all but 3.9  $\mu$ s of the 125  $\mu$ s frame. Similarly, DSTi input data is valid for only 3.9  $\mu$ s.

## **Digital Control Functions**

CSTi is a digital input (levels GNDD to  $V_{DD}$ ) which is used to control the function of the filter/codec. It operates in three different modes depending on the logic levels applied to the Control Address input (CA) and chip enable input (F1i) (see Table 1).

#### Mode 1

CA=-5V (V<sub>EE</sub>); CSTi=0V (GNDD)

The filter/codec is in normal operation with nominal transmit and receive gain of 0dB. The SD outputs are in their active states and the test modes cannot be entered.

$CA = -5V (V_{EE}); CSTi = +5V (V_{DD})$

A state of powerdown is forced upon the chip whereby DSTo becomes high impedance,  $V_R$  is connected to GNDA and all analog sections have power removed.

#### Mode 2

CA= -5V (V<sub>EE</sub>); CSTi receives an eight-bit control word

CSTi accepts a serial data stream synchronously with DSTi (i.e., it accepts an eight-bit serial word in a 3.9  $\mu$ s timeslot, updated every 125  $\mu$ s, and is specified identically to DSTi for timing considerations). This eight-bit control word is entered into Control Register A and enables programming of the following functions: transmit and receive gain, powerdown, loopback. Register B is reset to zero and the SD outputs assume their inactive state. Test modes cannot be entered.

### Mode 3

CA=0V (GNDD); CSTi receives an eight-bit control word

As in Mode 2, the control word enters Register A and the aforementioned functions are controlled. In this mode, however, Register B is not reset, thus not affecting the states of the SD outputs.

CA=+5V (V<sub>DD</sub>); CSTi receives an 8-bit control word

In this case the control word is transferred into Register B. Register A is unaffected. The input and output of PCM data is inhibited.

The contents of Register B controls the six uncommitted outputs SD0-SD5 (four outputs, SD0-SD3, on MT8960/61/64/65 versions of chip) and also provide entry into one of the three test modes of the chip.

Note: For Modes 1 and 2,  $\overline{F1i}$  must be at logic low for one period of 3.9 µs, in each 125 µs cycle, when PCM data is being input and output, and the control word at CSTi enters Register A. For Mode 3, F1i must be at a logic low for two periods of 3.9 µs, in each 125 µs cycle. In the first period, CA must be at GNDD or V<sub>EE</sub>, and in the second period CA must be high (V<sub>DD</sub>).

| Mode                                                                                                        | СА                                                                                  | CSTi            | Function                                                          |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------|--|--|--|--|

| 1                                                                                                           | $V_{EE}$                                                                            | GNDD            | Normal chip operation.                                            |  |  |  |  |

| (Note 1)                                                                                                    |                                                                                     | V <sub>DD</sub> | Powerdown.                                                        |  |  |  |  |

| 2                                                                                                           | $V_{EE}$                                                                            | Serial          | Eight-bit control word into Register A. Register B is reset.      |  |  |  |  |

|                                                                                                             |                                                                                     | Data            |                                                                   |  |  |  |  |

| 3                                                                                                           | GNDD                                                                                | Serial          | Eight-bit control word into register A. Register B is unaffected. |  |  |  |  |

| (Note 2)                                                                                                    |                                                                                     | Data            |                                                                   |  |  |  |  |

|                                                                                                             | V <sub>DD</sub>                                                                     | Serial          | Eight-bit control word into register A. Register B is unaffected. |  |  |  |  |

|                                                                                                             |                                                                                     | Data            |                                                                   |  |  |  |  |

| Note 1: When operating in Mode 1, there should be only one frame pulse ( $\overline{F1i}$ ) per 125 $\mu$ s |                                                                                     |                 |                                                                   |  |  |  |  |

| Note 2:                                                                                                     | When operating in Mode 3, PCM input and output is inhibited by CA=V <sub>DD</sub> . |                 |                                                                   |  |  |  |  |

Table 1 - Digital Control Modes

| BIT 2 | BIT 1  | BIT 0  | TRANSMIT (A/D)<br>FILTER GAIN (dB) |

|-------|--------|--------|------------------------------------|

| 0     | 0      | 0      | 0                                  |

| 0     | 0      | 1      | + 1                                |

| 0     | 1      | 0      | + 2                                |

| 0     | 1      | 1      | + 3                                |

| 1     | 0      | 0      | + 4                                |

| 1     | 0      | 1      | + 5                                |

| 1     | 1      | 0      | + 6                                |

| 1     | 1      | 1      | + 7                                |

| BIT 5 | BIT 4  | BIT 3  | RECEIVE (D/A)<br>FILTER GAIN (dB)  |

| 0     | 0      | 0      | 0                                  |

| 0     | 0      | 1      | - 1                                |

| 0     | 1      | 0      | - 2                                |

| 0     | 1      | 1      | - 3                                |

|       |        | t      |                                    |

| 1     | 0      | 0      | - 4                                |

| 1     | 0<br>0 | 0<br>1 | - 4<br>- 5                         |

| -     | _      | -      |                                    |

| BIT 2 | BIT 1 | BIT 0            | TRANSMIT (A/D)<br>FILTER GAIN (dB) |  |  |  |

|-------|-------|------------------|------------------------------------|--|--|--|

| BIT 7 | BIT 6 | FUNCTION CONTROL |                                    |  |  |  |

| 0     | 0     | Normal operation |                                    |  |  |  |

| 0     | 1     | Digital Loopback |                                    |  |  |  |

| 1     | 0     | Analog Loopback  |                                    |  |  |  |

| 1     | 1     |                  | Powerdown                          |  |  |  |

Table 2 - Control States - Register A

## Control Registers A, B

The contents of these registers control the filter/codec functions as described in Tables 2 and 3.

Bit 7 of the registers is the MSB and is defined as the first bit of the serial data stream input (corresponding to the sign bit of the PCM word).

On initial power-up these registers are set to the powerdown condition for a maximum of 25 clock cycles. During this time it is impossible to change the data in these registers.

## Chip Testing

By enabling Register B with valid data (eight-bit control word input to CSTi when  $\overline{F1i}$ =GNDD and CA= V<sub>CC</sub>) the chip testing mode can be entered. Bits 6 and 7 (most sign bits) define states for testing the transmit filter, receive filter and the codec function. The input in each case is V<sub>X</sub> input and the output in each case is V<sub>R</sub> output. (See Table 3 for details.)

## Loopback

Loopback of the filter/codec is controlled by the control word entered into Register A. Bits 6 and 7 (most sign bits) provide either a digital or analog loopback condition. Digital loopback is defined as follows:

- PCM input data at DSTi is latched into the PCM input register and the output of this register is connected to the input of the 3-state PCM output register.

- The digital input to the PCM digital-to-analog decoder is disconnected, forced to zero (0).

- The output of the PCM encoder is disabled and thus the encoded data is lost. The PCM output at DSTo is determined by the PCM input data.

Analog loopback is defined as follows:

- PCM input data is latched, decoded and filtered as normal but not output at V<sub>R</sub>.

- Analog output buffer at V<sub>R</sub> has its input shorted to GNDA and disconnected from the receive filter output.

- Analog input at V<sub>x</sub> is disconnected from the transmit filter input.

- The receive filter output is connected to the transmit filter input. Thus the decode signal is fed back through the receive path and encoded in the normal way. The analog output buffer at V<sub>R</sub> is not tested by this configuration.

In both cases of loopback, DSTi is the input and DSTo is the output.

### Logic Control Outputs SD0-5

These outputs are directly controlled by the logic states of bits 0-5 in Register B. A logic low (GNDD) in Register B causes the SD outputs to assume an inactive state. A logic high ( $V_{DD}$ ) in Register B causes the SD outputs to assume an active state (see Table 3). SD0-2 switch between GNDD and  $V_{DD}$  and may be used to control external logic or transistor circuitry, for example, that employed on the line card for performing such functions as relay drive for application of ringing to line, message waiting indication, etc.

SD3-5 are used primarily to drive external analog circuitry. Examples may include the switching in or out of gain sections or filter sections (e.g., ring trip filter) (Figure 7).

MT8962/63/66/67 provides all six SD outputs.

MT8960/61/64/65 each packaged in an 18-pin DIP provide only four control outputs, SD0-3.

Figure 6 - Typical Line Termination

| BITS  | <b>6 0-2</b> | LOGIC CONTROL OUTPUTS SD <sub>0</sub> -SD <sub>2</sub> |  |  |  |  |  |

|-------|--------------|--------------------------------------------------------|--|--|--|--|--|

| (     | )            | Inactive state - logic low (GNDD).                     |  |  |  |  |  |

| 1     |              | Active state - logic high (V <sub>DD</sub> ).          |  |  |  |  |  |

| BI    | Г З          | LOGIC CONTROL OUTPUT SD <sub>3</sub>                   |  |  |  |  |  |

| (     | )            | Inactive state - High Impedance.                       |  |  |  |  |  |

| 1     | l            | Active state - GNDA.                                   |  |  |  |  |  |

| BITS  | 6 4,5        | LOGIC CONTROL OUTPUTS $SD_4$ , $SD_5$                  |  |  |  |  |  |

| (     | )            | Inactive state - High Impedance.                       |  |  |  |  |  |

| 1     |              | Active state - GNDD.                                   |  |  |  |  |  |

| BIT 7 | BIT 6        | CHIP TESTING CONTROLS                                  |  |  |  |  |  |

| 0     | 0            | Normal operation.                                      |  |  |  |  |  |

| BIT | S 0-2 | LOGIC CONTROL OUTPUTS SD <sub>0</sub> -SD <sub>2</sub>                                                                                                                                                                 |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 1     | Transmit filter testing, i.e.: Transmit filter input connected to $V_X$ input Receive filter and Buffer disconnected from $V_R$                                                                                        |

| 1   | 0     | Receive filter testing, i.e.:<br>Receive filter input connected to V <sub>X</sub> input<br>Receive filter input disconnected from codec                                                                                |

| 1   | 1     | Codec testing i.e.:<br>Codec analog input connected to $V_X$<br>Codec analog input disconnected from transmit filter output<br>Codec analog output connected to $V_R$<br>$V_R$ disconnected from receive filter output |

#### Table 3 - Control States - Register B

#### Powerdown

Powerdown of the chip is achieved in several ways:

Internal Control:

- Initial Power-up. Initial application of V<sub>DD</sub> and V<sub>EE</sub> causes powerdown for a period of 25 clock cycles and during this period the chip will accept input only from C2i. The B-register is reset to zero forcing SD0-5 to be inactive. Bits 0-5 of Register A (gain adjust bits) are forced to zero and bits 6 and 7 of Register A become logic high thus reinforcing the powerdown.

- 2) Loss of C2i. Powerdown is entered 10 to 40  $\mu$ s after C2i has assumed a continuous logic high (V<sub>DD</sub>). In this condition the chip will be in the same state as in (1) above.

**Note:** If C2i stops at a continuous logic low (GNDD), the digital data and status is indeterminate.

#### External Control:

- 1) Register A. Powerdown is controlled by bits 6 and 7 (when both at logic high) of Register A which in turn receives its control word input via CSTi, when F1i is low and CA input is either at V<sub>EE</sub> or GNDD. Power is removed from the filters and analog sections of the chip. The analog output buffer at V<sub>R</sub> will be connected to GNDA. DSTo becomes high impedance and the clocks to the majority of the logic are stopped. SD outputs are unaffected and may be updated as normal.

- 2) CSTi Input. With CA at V<sub>EE</sub> and CSTi held at continuous logic high the chip assumes the same state as described in External Control (1) above.

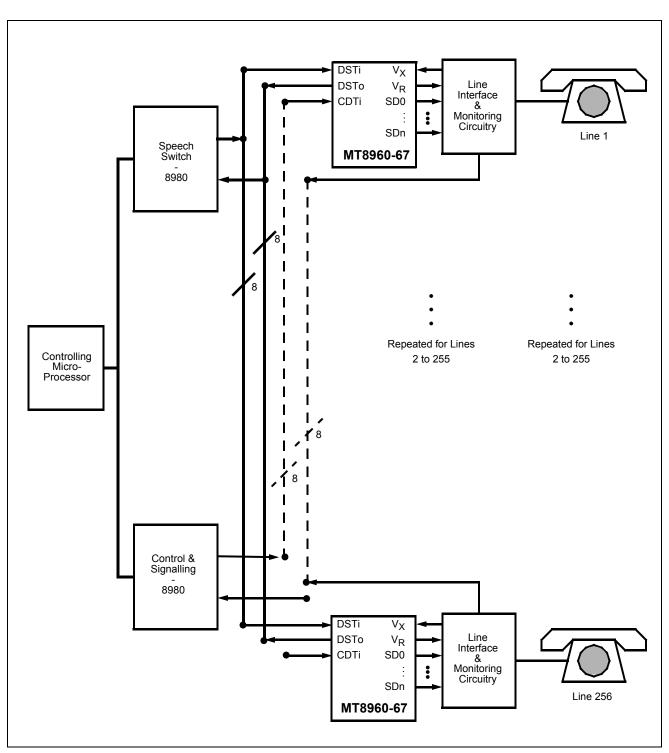

Figure 7 - Typical Use of the Special Drive Outputs

Figure 8 - Example Architecture of a Simple Digital Switching System using the MT8960-67

#### Absolute Maximum Ratings\*

|   | Parameter                                              | Symbol                | Min.                 | Max.                 | Units |

|---|--------------------------------------------------------|-----------------------|----------------------|----------------------|-------|

| 1 | DC Supply Voltages                                     | V <sub>DD</sub> -GNDD | -0.3                 | +6.0                 | V     |

|   |                                                        | V <sub>EE</sub> -GNDD | -6.0                 | +0.3                 | V     |

| 2 | Reference Voltage                                      | V <sub>Ref</sub>      | GNDA                 | V <sub>DD</sub>      | V     |

| 3 | Analog Input                                           | V <sub>X</sub>        | $V_{EE}$             | V <sub>DD</sub>      | V     |

| 4 | Digital Inputs                                         | Except CA             | GNDD-0.3             | V <sub>DD</sub> +0.3 | V     |

|   |                                                        | CA                    | V <sub>EE</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 5 | Output Voltage                                         | SD0-2                 | GNDD-0.3             | V <sub>DD</sub> +0.3 | V     |

|   |                                                        | SD3                   | V <sub>EE</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

|   |                                                        | SD4-5                 | V <sub>EE</sub> -0.3 | V <sub>DD</sub> +0.3 | V     |

| 6 | Current On Any Pin                                     | I <sub>I</sub>        |                      | 20                   | mA    |

| 7 | Storage Temperature                                    | Τs                    | -55                  | +125                 | °C    |

| 8 | Power Dissipation at 25°C (Derate 16 mW/°C above 75°C) | P <sub>Diss</sub>     |                      | 500                  | mW    |

\* Exceeding these values may cause permanent damage. Functional operation under these conditions is not implied.

|   | Characterist         | ics                                | Sym.                                 | Min.  | Тур.*        | Max.       | Units    | Comments                                                    |

|---|----------------------|------------------------------------|--------------------------------------|-------|--------------|------------|----------|-------------------------------------------------------------|

| 1 | Supply Voltage       |                                    | V <sub>DD</sub>                      | 4.75  | 5.0          | 5.25       | V        |                                                             |

|   |                      |                                    | $V_{EE}$                             | -5.25 | -5.0         | -4.75      | V        |                                                             |

|   |                      |                                    | V <sub>Ref</sub>                     |       | 2.5          |            | V        | See Note 1                                                  |

| 2 | Voltage On Digital G | round                              | VGNDD                                | -0.1  | 0.0          | +0.1       | Vdc      | Ref. to GNDA                                                |

|   |                      |                                    |                                      | -0.4  | 0.0          | +0.4       | Vac      | Ref. to GNDA 400 ns max. duration in 125 $\mu$ s cycle      |

| 3 | Operating Temperate  | ure                                | Τ <sub>Ο</sub>                       | 0     |              | +70        | °C       |                                                             |

| 4 | Operating Current    | V <sub>DD</sub><br>V <sub>EE</sub> | I <sub>DD</sub><br>I <sub>EE</sub>   |       | 3.0<br>3.0   | 4.0<br>4.0 | mA<br>mA | All digital inputs at $V_{DD}$ or GNDD (or $V_{EE}$ for CA) |

|   |                      | V <sub>Ref</sub>                   | I <sub>Ref</sub>                     |       | 2.0          |            | μA       | Mean current                                                |

| 5 | Standby Current      | V <sub>DD</sub><br>V <sub>EE</sub> | I <sub>DDO</sub><br>I <sub>EEO</sub> |       | 0.25<br>0.25 | 1.0<br>1.0 | mA<br>mA | All digital inputs at $V_{DD}$ or GNDD (or $V_{EE}$ for CA) |

**Note 1:** Temperature coefficient of  $V_{Ref}$  should be better than 100 ppm/°C.

**DC Electrical Characteristics** - Voltages are with respect to GNDD unless otherwise stated. T<sub>A</sub>=0 to 70°C, V<sub>DD</sub>=5V±5%, V<sub>EE</sub>=-5V±5%, V<sub>Ref</sub>=2.5V±0.5%, GNDA=GNDD=0V,Clock Frequency =2.048MHz. Outputs unloaded unless otherwise specified.

|        |        | Characteris                          | stics             | Sym.                   | Min.     | Тур.* | Max.                 | Units    | Test Conditions                  |

|--------|--------|--------------------------------------|-------------------|------------------------|----------|-------|----------------------|----------|----------------------------------|

| 1      |        | Input Current                        | Except CA         | I <sub>I</sub>         |          |       | 10.0                 | μA       | $V_{IN}$ = GNDD to $V_{DD}$      |

|        | -      |                                      | CA                | I <sub>IC</sub>        |          |       | 10.0                 | μA       | $V_{IN} = V_{EE}$ to $V_{DD}$    |

| 2      | D<br>I | Input Low                            | Except CA         | V <sub>IL</sub>        | 0.0      |       | 0.8                  | V        |                                  |

|        | G      | Voltage                              | CA                | V <sub>ILC</sub>       | $V_{EE}$ |       | V <sub>EE</sub> +1.2 | V        |                                  |

| 3      | <br>T  | Input High Voltage                   | All Inputs        | V <sub>IH</sub>        | 2.4      |       | 5.0                  | V        |                                  |

| 4      | A<br>L | Input Intermediate<br>Voltage        | CA                | V <sub>IIC</sub>       | 0.0      |       | 0.8                  | V        |                                  |

| 5      |        | Output Leakage<br>Current (Tristate) | DSTo<br>SD3-5     | I <sub>0Z</sub>        |          | ±0.1  | 10.0                 | μΑ<br>μΑ | Output High Impedance            |

| 6      | D      | Output Low                           | DSTo              | V <sub>OL</sub>        |          |       | 0.4                  | V        | I <sub>OUT</sub> =1.6 mA         |

|        | Ι      | Voltage                              | SD0-2             | V <sub>OL</sub>        |          |       | 1.0                  | V        | I <sub>OUT</sub> =1 mA           |

| 7      | G      | Output High                          | DSTo              | V <sub>OH</sub>        | 4.0      |       |                      | V        | Ι <sub>ΟUT</sub> =-100μΑ         |

|        | '<br>T | Voltage                              | SD0-2             | V <sub>OH</sub>        | 4.0      |       |                      | V        | I <sub>OUT</sub> =-1mA           |

| 8      | Α      | Output Resistance                    | SD3-5             | R <sub>OUT</sub>       |          | 1.0   | 2.0                  | KΩ       | V <sub>OUT</sub> =+1V            |

| 9      | L      | Output Capacitance                   | e DSTo            | C <sub>OUT</sub>       |          | 4.0   |                      | pF       | Output High Impedance            |

| 1<br>0 |        | Input Current                        | V <sub>X</sub>    | I <sub>IN</sub>        |          |       | 10.0                 | μA       | $V_{EE} \leq V_{IN} \leq V_{CC}$ |

| 1<br>1 | А      | Input Resistance                     | V <sub>X</sub>    | R <sub>IN</sub>        |          | 10.0  |                      | MΩ       |                                  |

| 1<br>2 | N<br>A | Input Capacitance                    | V <sub>X</sub>    | C <sub>IN</sub>        |          | 30.0  |                      | pF       | f <sub>IN</sub> = 0 - 4 kHz      |

| 1<br>3 | L<br>O | Input Offset Voltage                 | e V <sub>X</sub>  | V <sub>OSIN</sub>      |          | +1.0  |                      | mV       | See Note 2                       |

| 1<br>4 | G      | Output Resistance                    | V <sub>R</sub>    | R <sub>OUT</sub>       |          |       | 100                  | Ω        |                                  |

| 1<br>5 |        | Output Offset Volta                  | ge V <sub>R</sub> | V <sub>OSO</sub><br>UT |          |       | 100                  | mV       | Digital Input= +0                |

\* Typical figures are at 25°C with nominal ±5V supplies. For design aid only: not guaranteed and not subject to production testing.

Note 2:  $V_{OSIN}$  specifies the DC component of the digitally encoded PCM word.

AC Electrical Characteristics - Voltages are with respect to GNDD unless otherwise stated.  $T_A=0$  to 70°C,  $V_{DD}=5V\pm5\%$ ,  $V_{EE}=-5V\pm5\%$ ,  $V_{Ref}=2.5V\pm0.5\%$ , GNDA=GNDD=0V, Clock Frequency=2.048 MHz. Outputs unloaded unless otherwise specified.

|    |             | Characteristics                          |              | Sym.                                 | Min.     | Тур.* | Max        | Units    | Test Conditions                 |

|----|-------------|------------------------------------------|--------------|--------------------------------------|----------|-------|------------|----------|---------------------------------|

| 1  |             | Clock Frequency                          | C2i          | f <sub>C</sub>                       | 2.046    | 2.048 | 2.05       | MHz      | See Note 3                      |

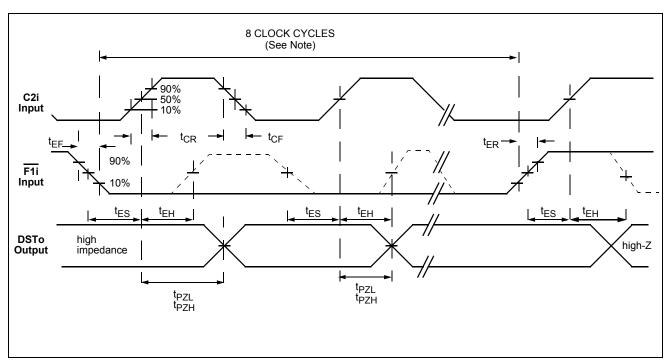

| 2  |             | Clock Rise Time                          | C2i          | t <sub>CR</sub>                      |          |       | 50         | ns       |                                 |

| 3  |             | Clock Fall Time                          | C2i          | t <sub>CF</sub>                      |          |       | 50         | ns       |                                 |

| 4  |             | Clock Duty Cycle                         | C2i          |                                      | 40       | 50    | 60         | %        |                                 |

| 5  |             | Chip Enable Rise Time                    | F1i          | t <sub>ER</sub>                      |          |       | 100        | ns       |                                 |

| 6  |             | Chip Enable Fall Time                    | F1i          | t <sub>EF</sub>                      |          |       | 100        | ns       |                                 |

| 7  |             | Chip Enable Setup Time                   | F1i          | t <sub>ES</sub>                      | 50       |       |            | ns       | See Note 4                      |

| 8  | D           | Chip Enable Hold Time                    | F1i          | t <sub>EH</sub>                      | 25       |       |            | ns       | See Note 4                      |

| 9  | Ι           | Output Rise Time                         | DSTo         | t <sub>OR</sub>                      |          |       | 100        | ns       |                                 |

| 10 | G           | Output Fall Time                         | DSTo         | t <sub>OF</sub>                      |          |       | 100        | ns       |                                 |

| 11 | '<br>Т<br>А | Propagation Delay Clock to Output Enable | DSTo         | t <sub>PZL</sub><br>t <sub>PZH</sub> |          |       | 122<br>122 | ns<br>ns | $\rm R_L$ =10 K\Omega to V_{CC} |

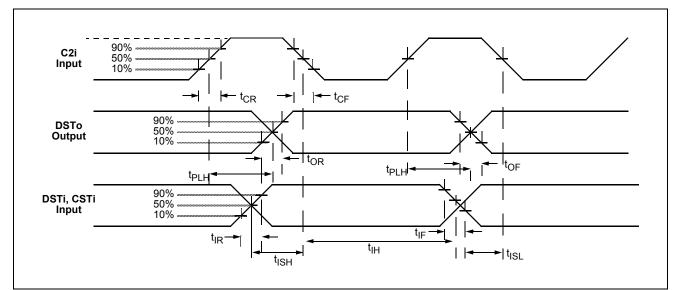

| 12 | L           | Propagation Delay<br>Clock to Output     | DSTo         | t <sub>PLH</sub><br>t <sub>PHL</sub> |          |       | 100<br>100 | ns<br>ns | C <sub>L</sub> =100 pF          |

| 13 |             | Input Rise Time                          | CSTi<br>DSTi | t <sub>IR</sub>                      |          |       | 100<br>100 | ns<br>ns |                                 |

| 14 |             | Input Fall Time                          | CSTi<br>DSTi | t <sub>IF</sub>                      |          |       | 100<br>100 | ns<br>ns |                                 |

| 15 |             | Input Setup Time                         | CSTi<br>DSTi | t <sub>ISH</sub><br>t <sub>ISL</sub> | 25<br>0  |       |            | ns<br>ns |                                 |

| 16 |             | Input Hold Time                          | CSTi<br>DSTi | t <sub>IH</sub>                      | 60<br>60 |       |            | ns<br>ns |                                 |

| 17 | D<br>I      | Propagation Delay<br>Clock to SD Output  | SD           | t <sub>PCS</sub>                     |          |       | 400        | ns       | C <sub>L</sub> = 100 pF         |

| 18 | G           | SD Output Fall Time                      | SD           | t <sub>SF</sub>                      |          |       | 200        | ns       | C <sub>L</sub> = 20 pF          |

| 19 | і<br>Т      | SD Output Rise Time                      | SD           | t <sub>SR</sub>                      |          |       | 400        | ns       |                                 |

| 20 | A<br>L      | Digital Loopback<br>Time DSTi to DSTo    |              | t <sub>DL</sub>                      |          |       | 122        | ns       |                                 |

(See Figures 9a, 9b, 9c)

\* Typical figures are at 25°C with nominal ±5V supplies. For design aid only: not guaranteed and not subject to production testing.

Note 3: The filter characteristics are totally dependent upon the accuracy of the clock frequency providing F1i is synchronized to C2i. The A/D and D/A functions are unaffected by changes in clock frequency.

Note 4: This gives a 75 ns period, 50 ns before and 25 ns after the 50% point of C2i rising edge, when change in F1i will give an undetermined state to the internally synchronized enable signal.

# AC Electrical Characteristics - Transmit (A/D) Path - Voltages are with respect to GNDD unless otherwise stated. $T_A=0$ to 70°C, $V_{DD}=5V\pm5\%$ , $V_{EE}=-5V\pm5\%$ , $V_{Ref}=2.5V\pm0.5\%$ , GNDA=GNDD=0V, Clock Frequency = 2.048MHz, Filter Gain Setting = 0dB. Outputs unloaded unless otherwise specified.

|    |           | Charact                                         | Sym.                                       | Min.             | Тур.<br>*                                 | Max.                   | Units                   | Test Conditions                    |                                                                                                  |

|----|-----------|-------------------------------------------------|--------------------------------------------|------------------|-------------------------------------------|------------------------|-------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|

| 1  |           | Analog Input at V<br>the overload deci<br>codec |                                            | V <sub>IN</sub>  |                                           | 4.82<br>9<br>5.00<br>0 |                         | V <sub>PP</sub><br>V <sub>PP</sub> | Level at codec:<br>μ-Law: 3.17 dBm0<br>A-Law: 3.14 dBm0<br>See Note 6                            |

| 2  |           | Absolute Gain (0                                | dB setting)                                | G <sub>AX</sub>  | -0.25                                     |                        | +0.25                   | dB                                 | 0 dBm0 @ 1004 Hz                                                                                 |

| 3  |           | Absolute Gain (+<br>settings)                   | 1dB to +7dB                                |                  | -0.35                                     |                        | +0.35                   | dB                                 | from nominal,<br>@ 1004 Hz                                                                       |

| 4  |           | Gain Variation                                  | With Temp                                  | G <sub>AXT</sub> |                                           | 0.01                   |                         | dB                                 | T <sub>A</sub> =0°C to 70°C                                                                      |

|    | А         |                                                 | With Supplies                              | G <sub>AXS</sub> |                                           | 0.04                   |                         | dB/V                               |                                                                                                  |

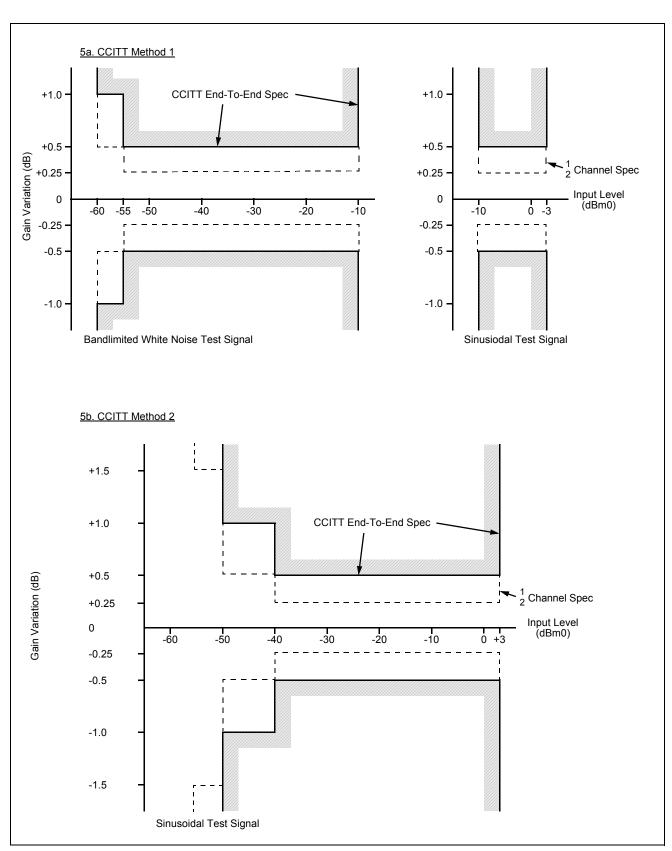

| 5  | N A L O G | Gain Tracking<br>(See Figure 12)                | CCITT G712<br>(Method 1)                   | GT <sub>X1</sub> | -0.25<br>-0.25<br>-0.50                   |                        | +0.25<br>+0.25<br>+0.50 | dB<br>dB<br>dB                     | Sinusoidal Level:<br>+3 to -20 dBm0<br>Noise Signal Level:<br>-10 to -55 dBm0<br>-55 to -60 dBm0 |

|    |           |                                                 | CCITT G712<br>(Method 2)<br>AT&T           | GT <sub>X2</sub> | -0.25<br>-0.50<br>-1.50                   |                        | +0.25<br>+0.50<br>+1.50 | dB<br>dB<br>dB                     | Sinusoidal Level:<br>+3 to -40 dBm0<br>-40 to -50 dBm0<br>-50 to -55 dBm0                        |

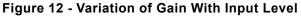

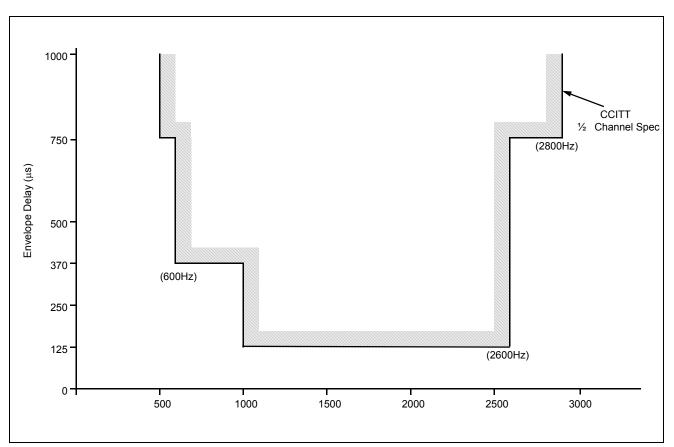

| 6  |           | Quantization<br>Distortion<br>(See Figure 13)   | CCITT G712<br>(Method 1)                   | D <sub>QX1</sub> | 28.00<br>35.60<br>33.90<br>29.30<br>14.20 |                        |                         | dB<br>dB<br>dB<br>dB<br>dB         | Noise Signal Level:<br>-3 dBm0<br>-6 to -27 dBm0<br>-34 dBm0<br>-40 dBm0<br>-55 dBm0             |

|    |           |                                                 | CCITT G712<br>(Method 2)<br>AT&T           | D <sub>QX2</sub> | 35.30<br>29.30<br>24.30                   |                        |                         | dB<br>dB<br>dB                     | Sinusoidal Input Level:<br>0 to -30 dBm0<br>-40 dBm0<br>-45 dBm0                                 |

| 7  |           | Idle Channel                                    | C-message                                  | N <sub>CX</sub>  |                                           |                        | 18                      | dBrnC0                             | μ-Law Only                                                                                       |

|    |           | Noise                                           | Psophometric                               | N <sub>PX</sub>  |                                           |                        | -67                     | dBm0p                              | CCITT G712                                                                                       |

| 8  |           | Single Frequency Noise                          |                                            | N <sub>SFX</sub> |                                           |                        | -56                     | dBm0                               | CCITT G712                                                                                       |

| 9  |           | Harmonic Distortion<br>(2nd or 3rd Harmonic)    |                                            |                  |                                           |                        | -46                     | dB                                 | Input Signal:<br>0 dBm0 @ 1.02 kHz                                                               |

| 10 |           | Envelope Delay                                  |                                            | D <sub>AX</sub>  |                                           |                        | 270                     | μS                                 | @ 1004 Hz                                                                                        |

| 11 |           | Envelope Delay<br>Variation With<br>Frequency   | 1000-2600 Hz<br>600-3000 Hz<br>400-3200 Hz | D <sub>DX</sub>  |                                           | 60<br>150<br>250       |                         | μs<br>μs<br>μs                     | Input Signal:<br>400-3200 Hz<br>Sinewave<br>at 0 dBm0                                            |

## AC Electrical Characteristics - Transmit (A/D) Path - Voltages are with respect to GNDD unless otherwise stated. $T_A=0$ to 70°C, $V_{DD}=5V\pm5\%$ , $V_{EE}=-5V\pm5\%$ , $V_{Ref}=2.5V\pm0.5\%$ , GNDA=GNDD=0V, Clock Frequency = 2.048MHz, Filter Gain Setting = 0dB. Outputs unloaded unless otherwise specified.

|    | A N A L O G | Quantization<br>Distortion<br>(cont'd)<br>(See Figure 13) | CCITT G712<br>(Method 2)<br>AT&T                                         | D <sub>QX2</sub>                               | 35.30<br>29.30<br>24.30                                 |                                                                           | dB<br>dB<br>dB                               | Sinusoidal Input Level:<br>0 to -30 dBm0<br>-40 dBm0<br>-45 dBm0          |

|----|-------------|-----------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------|

| 12 |             | Intermodulation<br>Distortion                             | CCITT G712<br>50/60 Hz                                                   | IMD <sub>X</sub>                               |                                                         | -55                                                                       | dB                                           | 50/60 Hz @ -23 dBm0<br>and any signal within<br>300-3400 Hz at -9<br>dBm0 |

|    |             |                                                           | CCITT G712<br>2 tone                                                     | IMD <sub>X</sub>                               |                                                         | -41                                                                       | dB                                           | 740 Hz and 1255 Hz<br>@ -4 to -21 dBm0.<br>Equal Input Levels             |

|    |             |                                                           | AT&T                                                                     | IMD <sub>X</sub><br>3                          |                                                         | -47                                                                       | dB                                           | 2nd order products                                                        |

|    |             |                                                           | 4 tone                                                                   | IMD <sub>X</sub>                               |                                                         | -49                                                                       | dB                                           | 3rd order products                                                        |

| 13 |             | Gain Relative to<br>Gain @ 1004 Hz<br>(See Figure 10)     | ≤50 Hz 60 Hz 200 Hz 300-3000 Hz 3200 Hz 3300 Hz 3400 Hz 4000 Hz ≥4600 Hz | G <sub>RX</sub>                                | -1.8<br>-<br>0.125<br>-<br>0.275<br>-<br>0.350<br>-0.80 | -25<br>-30<br>0.00<br>0.125<br>0.125<br>0.030<br>-<br>0.100<br>-14<br>-32 | dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB<br>dB | 0 dBm0 Input Signal<br>Transmit<br>Filter<br>Response                     |

| 14 |             | Crosstalk D/A to                                          | A/D                                                                      | CT <sub>RT</sub>                               |                                                         | -70                                                                       | dB                                           | 0 dBm0 @ 1.02 kHz<br>in D/A                                               |

| 15 |             | Power Supply<br>Rejection                                 | $V_{DD}$<br>$V_{EE}$                                                     | PSS<br>R <sub>1</sub><br>PSS<br>R <sub>2</sub> | 33<br>35                                                |                                                                           | dB<br>dB                                     | Input 50 mV <sub>RMS</sub> at<br>1.02 kHz                                 |

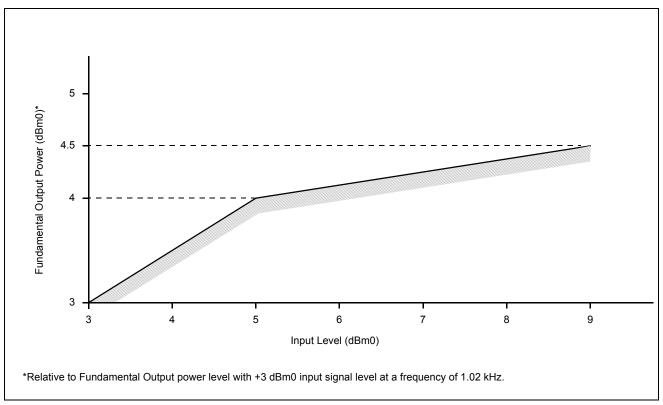

| 16 |             | Overload Dis<br>Fig.15)                                   | tortion (See                                                             |                                                |                                                         |                                                                           |                                              | Input<br>frequency=1.02kHz                                                |

Typical figures are at 25°C with nominal  $\pm$ 5V supplies. For design aid only: not guaranteed and not subject to production testing odBm0=1.185 V<sub>RMS</sub> for the  $\mu$ -Law codec. 0dBm0=1.231 V<sub>RMS</sub> for the A-Law codec. Note 6:

#### AC Electrical Characteristics - Receive (D/A) Path - Voltages are with respect to GNDD unless otherwise stated. $T_A=0$ to 70°C, $V_{DD}=5V\pm5\%$ , $V_{EE}=-5V\pm5\%$ , $V_{Ref}=2.5V\pm0.5\%$ , GNDA=GNDD=0V, Clock Frequency = 2.048MHz, Filter Gain Setting = 0dB. Outputs unloaded unless otherwise specified.

|    |                  | Characteristics                                                                          |                                    | Sym.              | Min.                                      | Тур.*          | Max.                    | Units                              | Test Conditions                                                                                  |

|----|------------------|------------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------------------------------|----------------|-------------------------|------------------------------------|--------------------------------------------------------------------------------------------------|

| 1  |                  | Analog output at V <sub>R</sub><br>equivalent to the overload<br>decision level at codec |                                    | V <sub>OUT</sub>  |                                           | 4.829<br>5.000 |                         | V <sub>pp</sub><br>V <sub>pp</sub> | Level at codec:<br>μ-Law: 3.17 dBm0<br>A-Law: 3.14 dBm0<br>R <sub>L</sub> =10 KΩ<br>See Note 7   |

| 2  |                  | Absolute Gain (0                                                                         | dB setting)                        | G <sub>AR</sub>   | -0.25                                     |                | +0.25                   | dB                                 | 0 dBm0 @ 1004Hz                                                                                  |

| 3  |                  | Absolute Attenua<br>to -7dB settings)                                                    | <b>`</b>                           |                   | -0.35                                     |                | +0.35                   | dB                                 | From nominal,<br>@ 1004Hz                                                                        |

| 4  |                  | Gain Variation                                                                           | With Temp.                         | G <sub>ART</sub>  |                                           | 0.01           |                         | dB                                 | T <sub>A</sub> =0°C to 70°C                                                                      |

|    |                  |                                                                                          | With Supplies                      | G <sub>ARS</sub>  |                                           | 0.04           |                         | dB/V                               |                                                                                                  |

| 5  |                  | Gain Tracking<br>(See Figure 12)                                                         | CCITT G712<br>(Method 1)           | GT <sub>R1</sub>  | -0.25<br>-0.25<br>-0.50                   |                | +0.25<br>+0.25<br>+0.50 | dB<br>dB<br>dB                     | Sinusoidal Level:<br>+3 to -10 dBm0<br>Noise Signal Level:<br>-10 to -55 dBm0<br>-55 to -60 dBm0 |

|    | A<br>N           |                                                                                          | CCITT G712<br>(Method 2)<br>AT & T | GT <sub>R2</sub>  | -0.25<br>-0.50<br>-1.50                   |                | +0.25<br>+0.50<br>+1.50 | dB<br>dB<br>dB                     | Sinusoidal Level:<br>+3 to -40 dBm0<br>-40 to -50 dBm0<br>-50 to -55 dBm0                        |

| 6  | A<br>L<br>O<br>G | Quantization<br>Distortion<br>(See Fig. 13)                                              | CCITT G712<br>(Method 1)           | D <sub>QR1</sub>  | 28.00<br>35.60<br>33.90<br>29.30<br>14.30 |                |                         | dB<br>dB<br>dB<br>dB<br>dB         | Noise Signal Level:<br>-3 dBm0<br>-6 to -27 dBm0<br>-34 dBm0<br>-40 dBm0<br>-55 dBm0             |

|    |                  |                                                                                          | CCITT G712<br>(Method 2)<br>AT & T | D <sub>QR2</sub>  | 36.40<br>30.40<br>25.40                   |                |                         | dB<br>dB<br>dB                     | Sinusoidal Input Level:<br>0 to -30 dBm0<br>-40 dBm0<br>-45 dBm0                                 |

| 7  |                  | Idle Channel                                                                             | C-message                          | N <sub>CR</sub>   |                                           |                | 12                      | dBrnC0                             | μ-Law Only                                                                                       |

|    |                  | Noise                                                                                    | Psophometric                       | N <sub>PR</sub>   |                                           |                | -75                     | dBm0p                              | CCITT G712                                                                                       |

| 8  |                  | Single Frequenc                                                                          | y Noise                            | N <sub>SFR</sub>  |                                           |                | -56                     | dBm0                               | CCITT G712                                                                                       |

| 9  |                  | Harmonic Distortion<br>(2nd or 3rd Harmonic)                                             |                                    |                   |                                           |                | -46                     | dB                                 | Input Signal 0 dBm0<br>at 1.02 kHz                                                               |

| 10 |                  | Intermodulation<br>Distortion                                                            | CCITT G712<br>2 tone               | IMD <sub>R2</sub> |                                           |                | -41                     | dB                                 |                                                                                                  |

|    |                  |                                                                                          | AT & T                             | IMD <sub>R3</sub> |                                           |                | -47                     | dB                                 | 2nd order products                                                                               |

|    |                  |                                                                                          | 4 tone                             | IMD <sub>R4</sub> |                                           |                | -49                     | dB                                 | 3rd order products                                                                               |

#### AC Electrical Characteristics - Receive (D/A) Path - Voltages are with respect to GNDD unless otherwise stated. $T_A=0$ to 70°C, $V_{DD}=5V\pm5\%$ , $V_{EE}=-5V\pm5\%$ , $V_{Ref}=2.5V\pm0.5\%$ , GNDA=GNDD=0V, Clock Frequency = 2.048MHz, Filter Gain Setting = 0dB. Outputs unloaded unless otherwise specified.

| 11 |                            | Envelope Delay                                                     |                                    | D <sub>AR</sub>      |                                   |                  | 210                                                 | μS                               | @ 1004 Hz                                                    |

|----|----------------------------|--------------------------------------------------------------------|------------------------------------|----------------------|-----------------------------------|------------------|-----------------------------------------------------|----------------------------------|--------------------------------------------------------------|

| 12 |                            | Envelope Delay 1000-2<br>Variation with 600-30<br>Frequency 400-32 | 00 Hz                              | D <sub>DR</sub>      |                                   | 90<br>170<br>265 |                                                     | μs<br>μs<br>μs                   | Input Signal:<br>400 - 3200 Hz digital<br>sinewave at 0 dBm0 |

| 13 | A<br>N<br>A<br>L<br>O<br>G | 3300<br>3400<br>4000                                               | Hz<br>3000 Hz<br>) Hz<br>) Hz      | G <sub>RR</sub>      | -0.5<br>-0.125<br>-0.350<br>-0.80 |                  | 0.125<br>0.125<br>0.030<br>-0.100<br>-14.0<br>-28.0 | dB<br>dB<br>dB<br>dB<br>dB<br>dB | 0 dBm0 Input Signal<br>Receive<br>Filter<br>Response         |

| 14 | G                          | Crosstalk A/D to D/A                                               |                                    | CT <sub>TR</sub>     |                                   |                  | -70                                                 | dB                               | 0 dBm0 @ 1.02 kHz<br>in A/D                                  |

| 15 |                            |                                                                    | / <sub>DD</sub><br>/ <sub>EE</sub> | $PSRR_3$<br>$PSRR_4$ | 33<br>35                          |                  |                                                     | dB<br>dB                         | Input 50 mV <sub>RMS</sub> at<br>1.02 kHz                    |

| 16 |                            | Overload Distortion<br>(See Fig. 15)                               |                                    |                      |                                   |                  |                                                     |                                  | Input frequency=1.02<br>kHz                                  |

\* Typical figures are at 25°C with nominal  $\pm$ 5V supplies. For design aid only: not guaranteed and not subject to production testing. **Note 7:** 0dBm0=1.185 V<sub>RMS</sub> for  $\mu$ -Law codec and 0dBm0=1.231 V<sub>RMS</sub> for A-Law codec.

Figure 9a - Timing Diagram - 125  $\mu$ s Frame Period

## Figure 9b - Timing Diagram - Output Enable

Note: In typical applications,  $\overline{F1i}$  will remain low for 8 cycles of C2i. However, the device will function normally as long as t<sub>ES</sub> and t<sub>EH</sub> are met at each positive edge of C2i.

Figure 9c - Timing Diagram - Input/Output

Figure 10 - Attenuation vs Frequency for Transmit (A/D) Filter

Figure 11 - Attenuation vs Frequency for Receive (D/A) Filter

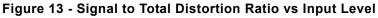

Figure 14 - Envelope Delay Variation Frequency

Figure 15 - Overload Distortion (End-to-End)

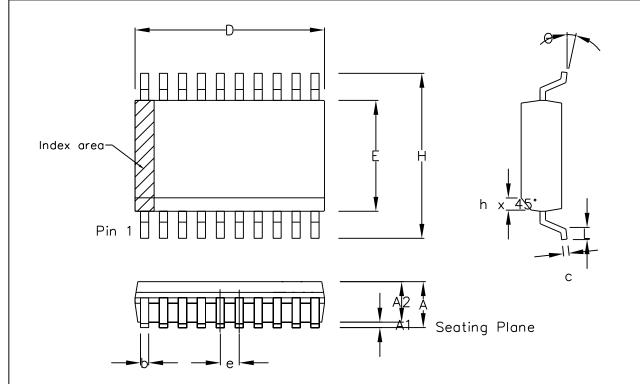

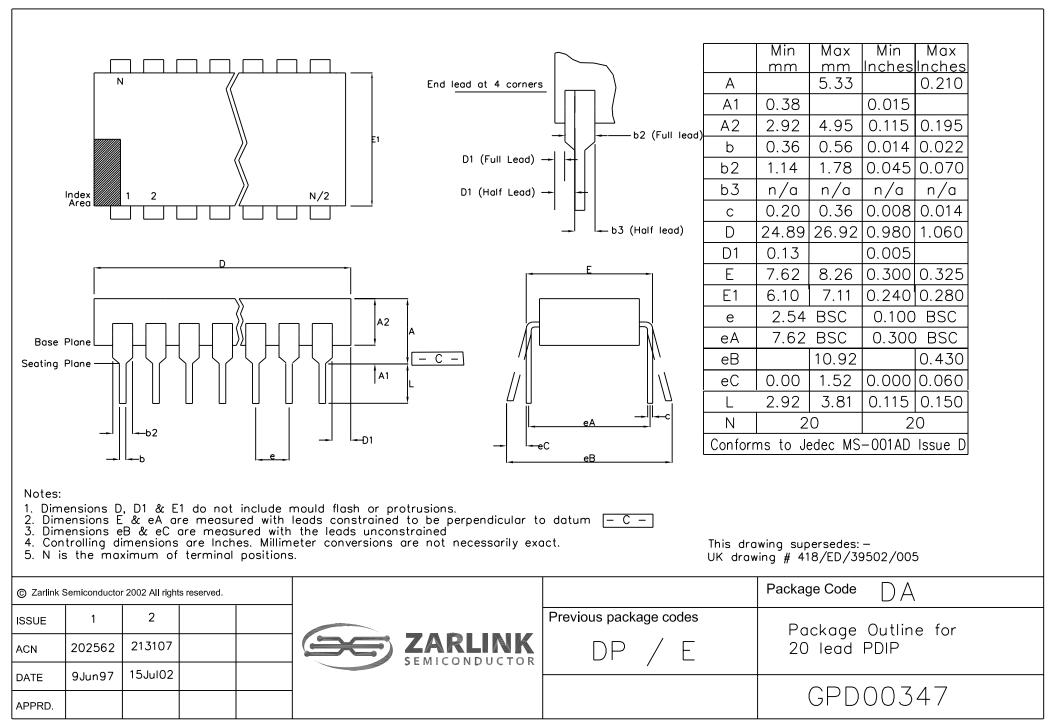

|        |              | ol Dime  |       |    | Altern. Dimensions |         |       |  |  |

|--------|--------------|----------|-------|----|--------------------|---------|-------|--|--|

| Symbol | in ı         | millimet | res   |    | in inches          |         |       |  |  |

| ,      |              | Nominal  | MAX   |    | MIN                | Nominal | MAX   |  |  |

| Α      | 2.35         |          | 2.65  |    | 0.093              |         | 0.104 |  |  |

| A1     | 0.10         |          | 0.30  |    | 0.004              |         | 0.012 |  |  |

| A2     | 2.25         |          | 2.35  |    | 0.089              |         | 0.092 |  |  |

| D      | 12.60        |          | 13.00 |    | 0.496              |         | 0.512 |  |  |

| Н      | 10.00        |          | 10.65 |    | 0.394              |         | 0.419 |  |  |

| Ε      | 7.40         |          | 7.60  |    | 0.291              |         | 0.299 |  |  |

| L      | 0.40         |          | 1.27  |    | 0.016              |         | 0.050 |  |  |

| е      | 1.1          | 27 BS    | C.    |    | 0.050 BSC.         |         |       |  |  |

| b      | 0.33         |          | 0.51  |    | 0.013              |         | 0.020 |  |  |

| С      | 0.23         |          | 0.32  |    | 0.009              |         | 0.013 |  |  |

| θ      | 0°           |          | 8°    |    | 0°                 |         | 8°    |  |  |

| h      | 0.25         |          | 0.75  |    | 0.010              |         | 0.029 |  |  |

|        | Pin features |          |       |    |                    |         |       |  |  |

| Ν      | 20           |          |       |    |                    |         |       |  |  |

| Cor    | form         | s to .   | JEDEC | MS | -013               | AC Iss  | s. C  |  |  |

#### Notes:

- 1. The chamfer on the body is optional. If it not present, a visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimension are in millimeters.

- Dimension D do not include mould flash, protrusion or gate burrs. These shall not exceed 0.006" per side.

Dimension E1 do not include inter-lead flash or protrusion. These shall not exceed 0.010" per side.

Dimension b does not include dambar protrusion/intrusion. Allowable dambar protrusion shall be 0.004"

- total in excess of b dimension.

| © Zarlink Semiconductor 2002 All rights reserved. |        |         |         |  |               |                        | Package Code                        |  |  |

|---------------------------------------------------|--------|---------|---------|--|---------------|------------------------|-------------------------------------|--|--|

| ISSUE                                             | 1      | 2       | 3       |  |               | Previous package codes | Package Outline for                 |  |  |

| ACN                                               | 6746   | 201941  | 213098  |  | SEMICONDUCTOR | MP/S                   | 20 lead SOIC<br>(0.300" Body Width) |  |  |

| DATE                                              | 7Apr95 | 27Feb97 | 15Jul02 |  |               |                        |                                     |  |  |

| APPRD.                                            |        |         |         |  |               |                        | GPD00015                            |  |  |

## For more information about all Zarlink products visit our Web Site at

#### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's l2C components conveys a licence under the Philips l2C Patent rights to use these components in and l2C System, provided that the system conforms to the l2C Standard Specification as defined by Philips.